利用屏蔽栅极功率 MOSFET 技术降低传导和开关损耗

监管机构与终端客户对DC/DC电源效率的要求越来越高。新的设计要求更低的导通阻抗,同时不能影响非钳位电感性开关(UIS)能力或者不增加开关损耗。屏蔽栅极MOSFET可为30~200V范围的DC/DC电源设计人员提供相关解决方案。现在,通过提高开关性能,导通阻抗Rds(on)已能降低50%及以上,从而提高效率,为更高频率工作创造条件。本文讨论了屏蔽栅极MOSFET在中等电压MOSFET(40~300V)应用中的优势。

本文引用地址:https://www.eepw.com.cn/article/179302.htm电源设计挑战

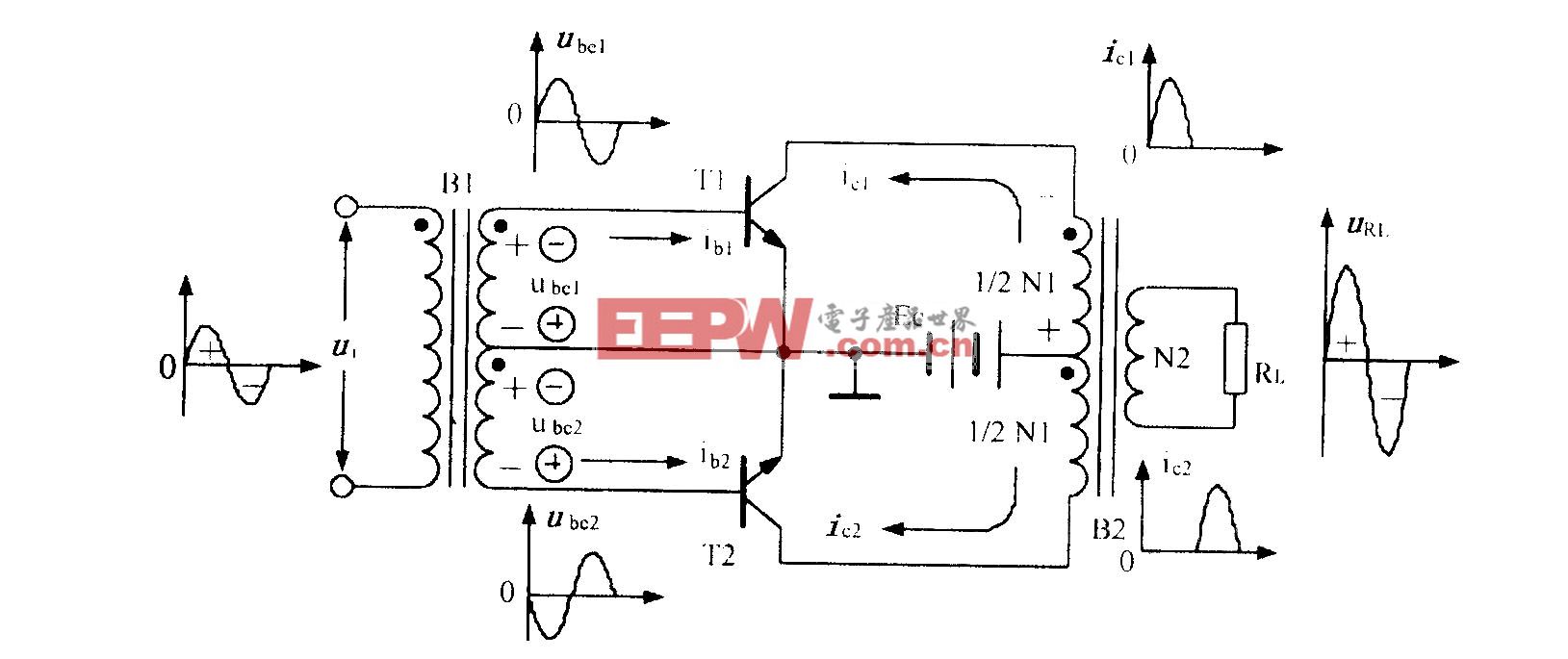

DC/DC设计人员一直面临着提高效率和功率密度的挑战。而功率MOSFET技术的不断进步帮助他们得以实现这一目标。导通阻抗Rds(on)和栅极电荷Qg中,一般总是一个减小则另一个增大,故功率MOSFET设计人员必须考虑到二者之间的权衡。一种新的沟槽MOSFET工艺可以做到减小Rds(on),却不影响Qg。这种技术就是屏蔽栅极技术。它能够减小中压MOSFET中导通阻抗的关键分量——与漏源击穿电压(BVdss)有关的外延阻抗(epi resistance)。如图1所示,这种技术特别适用于大于100V的应用领域。

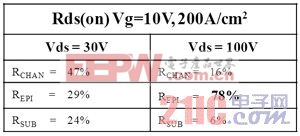

图1 传统沟槽技术中Rds(on)的各个分量

图1所示为额定30V与100V的传统沟槽MOSFET的Rds(on)分量的比较。对于100V的器件,Rds(on)中外延分量百分比要大得多。而利用屏蔽栅极这样的电荷平衡技术,外延阻抗可降低一半以上,同时不会增加总的Qg或Qgd分量。

电荷平衡技术

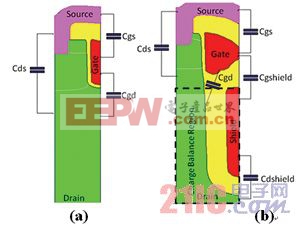

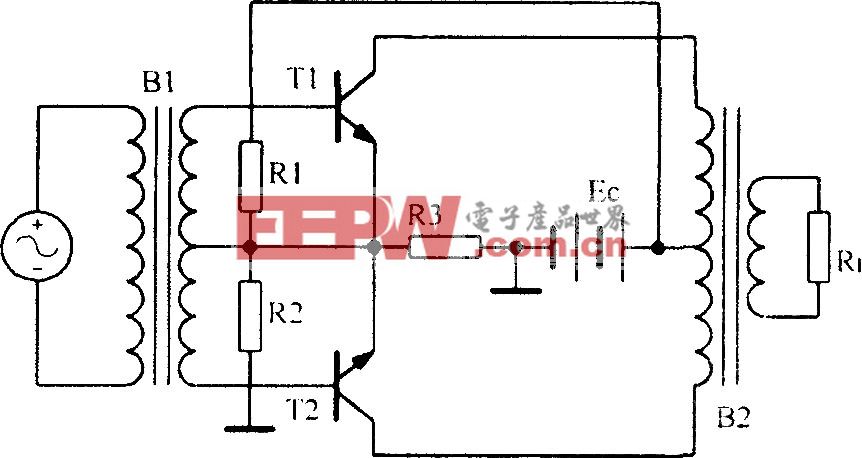

图2对传统器件与屏蔽栅极沟槽器件的横截面进行了比较。后者通过整合一个屏蔽电极来实现电荷平衡,支持该电压区域的阻抗和长度都被减小,从而大幅降低Rds(on)。

图2 (a)传统器件

(b)屏蔽栅极电荷平衡沟槽结构

此外,屏蔽电极位于栅极电极之下,后者把传统沟槽MOSFET底部的大部分栅漏极电容(Cgd或Crss)都转换为栅源极电容(Cgs)。于是,屏蔽电极就把栅极电极与漏极电势隔离开来。

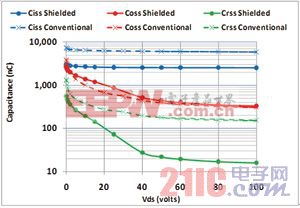

图3比较了具有相等Rds(on)的传统MOSFET与屏蔽栅极沟槽MOSFET的电容分量。由于Crss减小,从关断切换到导通状态,或从导通切换到关断状态所需的时间缩短,开关损耗因此被降至最低。特别地,如图4所示,减小Qgd,可把器件同时加载高压和大电流的时间缩至最短,从而减小开关能耗。

图3 在20A Rds(on) 5.7mΩ的相同条件下,传统器件与屏蔽栅极沟槽器件的电容分量的比较

评论