基于NAND FLASH的大容量视频存储系统的设计

摘要:针对MPEG4格式压缩的视频数据,给出了采用NAND FLASH为存储介质,以FPGA为存储阵列的控制器,并用DSF作为数据处理的核心单元,来完成大容量视频数据存储的系统设计方法,同时对坏块的检测处理等关键问题提出了解决方案。

关键词:FPGA;DSP FLASH;大容量;存储

0 引言

科技的发展,尤其是航空、航天、航海技术的发展,对于科研设备所拍摄的视频数据以及设备运行情况的监视录像,都迫切地需要一种容量大、速度快、存储性能可靠的图像存储设备。传统的存储介质主要以早期的磁带机和其后的磁盘为主,由于磁带机存储密度低,存储内容不易查找,已经退出了历史舞台。而磁盘受到强烈震动后容易丢失数据,严重制约了它在航空、航天、航海领域中的应用。与传统的硬盘相比,NADN FLASH作为一种新兴的半导体存储器件具有存储密度高、可靠性高、体积小、质量轻、功耗小、寿命长、无噪声、抗震动、能适应恶劣的力学和温度环境等优点。由此可见,基于NADN FLASH的大容量存储系统的研究具有更为重要的意义。

1 系统概述

本系统以ADI公司的高性能DSP芯片BF533为核心,用并行外围接口(PPI)来接收中心控制板的视频数据和控制命令,并将处理结果和存储在介质中的视频数据传输给中心控制板;以Sumsung公司的NAND FLASH芯片K9WBG08U1M为存储介质;用Altera公司的FPGA芯片EP2C35来实现对FLASH的时序控制。根据实际需求,本系统使用了100片K9WBG08U1M芯片,存储深度可达400GB,其安全存储速率可达5MB/s。该系统的视频数据采用文件的形式来管理,即每个视频文件都有一个文件表项,里面包含文件名称、文件地址以及文件大小等信息,此表项存放在FLASH的文件列表中,在进行存储、下载、剪切、删除等操作时,都需要将文件列表读到DSP的SDRAM中,以确定目标文件的地址,从而进行后续处理。

2 系统硬件设计

2.1 芯片的选择

K9WBG08U1M芯片通过8位复用的I/O总线多周期输入寻址,即共分5个周期,前2个周期输入A0~A11的页内地址(列地址),后3个周期输入A12~A30的页地址(行地址)。其单片存储容量为(4G+128M)B,内部由两片K9KAG08U0M芯片构成,而K9KAG08U0M芯片又分为8 192块,每块64页,每页(4 K+128)B。该芯片以页为单位来进行编程和读操作,典型编程时间为200μs,最大编程时间为700μs,最小写周期为25 ns,最小串行读周期为50 ns;以块为单位进行擦除,典型擦除时间为1.5 ms。其内部有一个页寄存器,在进行编程和读操作时,先将要写或要读的一页数据缓存到页寄存器中,然后写入编程命令开始页编程或发送读使能信号开始串行读。由此可以计算出FLASH的最快写入速率为4 096 B/(200μs+4 096×25 ns)≈13 Mb/s,安全写入速率为4 096 B/(700μs+4 096×25 nS)≈5 Mb/s。考虑到数据的安全写入,我们选取了最大编程时间700μs,即安全写入速率为5MB/s。

2.2 系统硬件结构框图

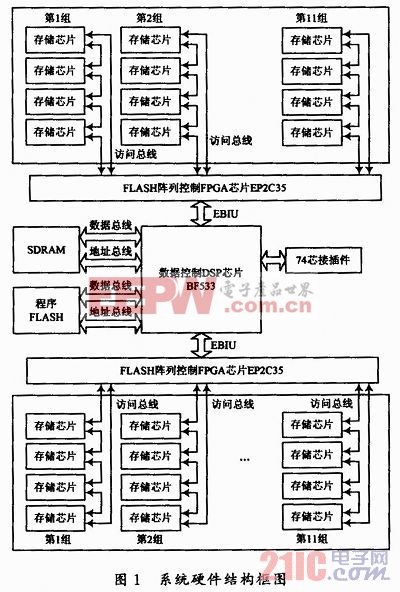

本系统作为网络视频存储系统的子系统,通过DSP的半双工接口PPI与中心控制板进行通信。首先将接收到的数据缓存在SDRAM中,然后对缓存下来的数据进行分析,辨别命令类型后进行与命令相应的操作,同时通过UART这个低速通道向中心控制板返回实时状态信息。其硬件结构框图如图1所示。

评论