基于STD总线的多路数字I/O设计

3.1 部分程序代码

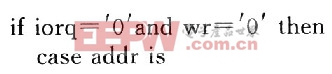

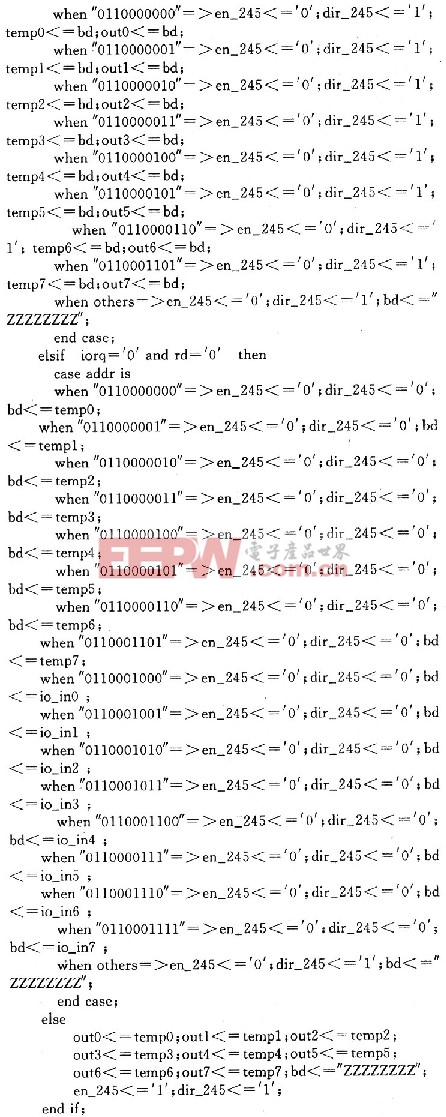

部分程序代码如下:

其中:addr是10位地址总线;bd是8位数据总线;en_245和dir_245分别是STD总线接口芯片74LS245的片选使能与方向信号;tempx是片内寄存器;io_inx和outx分别是8位输入、8位输出I/O口。

3.2 性能描述

多路数字I/O口的选择由10位地址决定,不同的地址操作不同的。I/O端口,在I/O非动态情况下,数据总线处于高阻状态,避免了总线冲突,同时也提高了I/O端口的稳定性,减少了高速数据传输条件下引起不必要的错误,根据现场对I/O输入、输出的需要,可以修改程序,灵活改变端口的功能,另外,对于输出端口,加入了数据写出后读回的功能,使得上位机能够随时验证写出数据的正确性,对于外设信号,通过信号调理板实现电平匹配,进一步增加了本设计的功能可靠性。

4 结语

以CPLD器件为核心,选用Xilinx公司的ISE作为硬件开发平台,并采用VHDL编程语言,充分应用了可编程逻辑器件的特点,发挥了VHDL硬件描述语言的编程优点。减少了芯片数量,既做到了系统小型化又降低了成本。程序已通过综合实验,应用了STD总线的通讯特点,与总线上的其他板卡、设备通讯也极为方便,既解决了工业通信网络的一般问题,又达到了工业通用I/O的较高要求。总之,该多路数字I/O设计容量高、功耗低、速度快,不仅具有通用性、实用性,而且具有灵活性和移植性,便于调试,为高速I/O开发设计提供了一种很好的尝试,相信在很多行业都会有广阔的应用前景。本文引用地址:https://www.eepw.com.cn/article/162940.htm

评论