基于中档FPGA多相滤波器的设计实现

相比之下, FIR滤波器没有反馈,这意味着它的脉冲响应在一个有限的时间范围之内。 FIR滤波器拥有优于IIR滤波器的几个优点,其中包括一个事实,即在整个频谱范围,他们有完全恒定的群时延,在所有频率范围内,不论滤波器的大小,他们是完全稳定的。

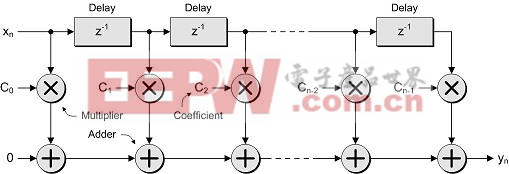

通用FIR滤波器的图形表示如图10所示。在这种情况下,输入样本xn通过一系列的缓冲寄存器(这些都标记为z-1,对应延时单元的Z变换)。

图10 经典FIR滤波器的通用表示

滤波器的工作原理是用一系列的常数(称为抽头系数)乘以一系列最新的n个数据采样,并对所得到的数组的单元进行求和。通过改变系数和滤波器抽头数目的加权(值),FIR滤波器实际上可实现几乎任何所需的频率响应特性。

问题是FIR滤波器可能需要大量的抽头(有时数百个),以实现其预定的目标。每一个抽头需要消耗逻辑资源的乘法器累加器( Mac )单元。另外在每个时钟,每个抽头执行消耗功率2的乘法和加操作。

用多相FIR滤波器进行抽取

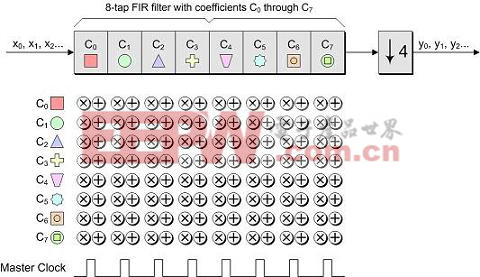

多相滤波器的基本概念是把FIR滤波器分割成若干较小的单元,然后组合这些单元的结果。首先,让我们考虑一个基于常规8抽头FIR滤波器的抽取子系统的符号表示,如图11所示(为了使用这些例子,我们假设抽取因子为M = 4 )。

图11 基于传统的8抽头FIR滤波器的抽取器的符号表示

现在让我们假设主时钟正在以某一频率fHz运行。像往常一样,在滤波操作之后任何不要的样本将被丢弃,但这样做是低效率的,因为这意味着是以完全的时钟频率在进行滤波。用另一种方式来看这种操作,即在每个时钟时刻,每个抽头级执行乘法和加运算。

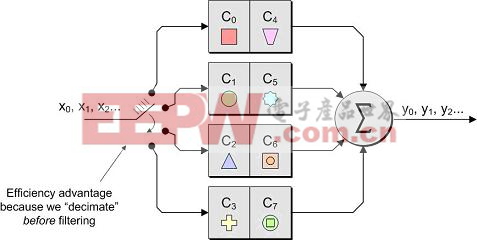

相比多相实现的情况,我们可以将原来的8抽头FIR滤波器分为四个2抽头子滤波器,如图12所示。

图12 基于4 × 2抽头多相滤波器的抽取器的符号表示

假设同样的主时钟以f Hz的频率运行,我们可以想象输入数据流被送入一个旋转开关(当然,这可用标准的逻辑技术来实现)。第一个数据值送入第一个子滤波器;第二个数据值送入第二个子滤波器;第三个数据值送入第三个子滤波器;第四个数据值送入第四个子滤波器。然后,我们进行“循环”操作,以便第五个数据值送入第一个子滤波器;第六个数据值送入第二个子滤波器;等等。

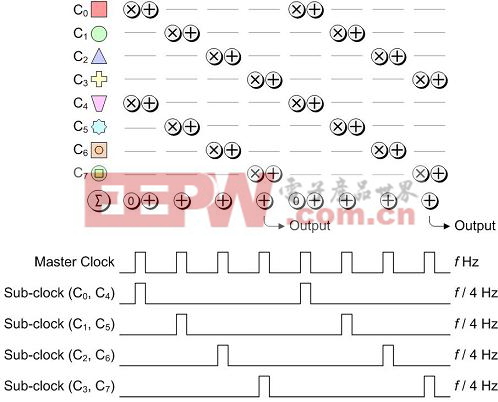

使用子滤波器减少了可能的饱和/溢出(发生任何饱和/溢出通常只需要在最后的函数求和时进行处理)。另外,使用子滤波器具有一个直接有效的优点,因为在执行滤波操作之前,我们有效地“抽取”了数据。这也意味着,我们的四个子滤波器中的每个都能有效地以F ÷ 4Hz的频率运行,如图13所示。

图13 4 × 2抽头多相滤波器的运行情况

评论