基于DSP+FPGA的红外图像小目标检测系统设计

2.2 存储模块

TS201的片上存储器分为两个部分:每个内核各使用100 KB的专用、高速L1存储器;128 KB的大容量共享L2存储器。通过EBIU接口外扩SDRAM和Flash两种存储器。选取2片MT48L32M16A2来构成SDRAM存储器,图像处理数据和图像处理中间结果可存储在SDRAM中。系统扩展64 MB的Flash,选用S29GL064M90T,主要存放DSP内核程序。

FPGA的存储系统:选取2片IS61LV10248来构成SRAM存储器,主要用于存储从SAA7111传输到FPGA的数据,根据视频数据的奇偶场的关系,在数据的存取过程中采用乒乓存取方式,当SRAM1存储数据的时候,FPGA从SRAM2读取数据,传给SAA7121做为显示使用,当SRAM2存储数据的时候,FPGA从SRAM1读取数据,传给SAA7121做为显示使用,同时通过对读时钟和读范围的控制,可以控制图像的现实范围和现实方式。具体硬件连接结构如图5所示。

2.3 DSP双核以及FPGA之间的通信

在本系统中,涉及到TS201两个核之间的通信以及TS201与FPGA之间的通信。FPGA给DSP提供预处理之后的图像数据,DSP根据提供的图像数据进行目标检测算法,并将检测之后的坐标数据传输到FPGA,FPGA将坐标信息叠加到原始图像后送给SAA7121显示。常见的双核通信主要采用中断、轮询两种通信方式。中断是利用两个核的中断机制来实现FPGA与DSP之间的通信;轮询是通过在双核的共享寄存器里设置一些信号量,供双核通信与访问。考虑到本系统的应用条件,采用轮询的通信方式,DSP的异步存储器的地址空间映射到FPGA,通过FPGA操作数据线和地址线,即可完成FPGA与DSP之间的数据交互。

2.4 系统工作流程

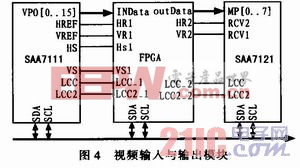

整个系统的工作流程为:由CCD采集视频模拟信号,经过可编程视频解码处理器SAA7111解码后输出场同步、行同步、像素时钟和位宽为16 bit的数字图像信号,并将信号送入FPGA中,在FPGA中对送来的数据做缓存,预处理,再通过与TS201连接的双向LINKPORT,把图像数据实时地导入DSP中,在DSP中运行检测算法,得到被检测目标的正确坐标,DSP把目标的坐标信息返回到FPGA中,FPGA根据坐标信息在原始图像上标示出目标的位置,最后将处理后的图像信号传给可编程视频编码器SAA7121进行编码实现D/A转换,输出模拟视频,并把检测结果显示在视频显示设备上。

3 结论

首先研究了形态学Top-hat算子,并利用Top-hat算子进行背景抑制,同时,采用最大类间方差法获得图像的阈值,分割背景和目标,实现小目标检测,通过仿真实验发现,这种方法能够在一定程度上减少实际检测中的虚警率,增加目标检测的准确性。

利用DSP+FPGA的系统架构设计了实现算法的硬件平台,这种结构在一定程度上可以满足实时性和灵活性的要求,具有很强的通用性和可扩展性。并在设计中采用了模块化设计,这样的设计便于集中控制,能够节省程序运行时间。

评论