基于DSP+FPGA的红外图像小目标检测系统设计

为节约程序运行时间,选取k的取值范围为[μ+5σ…N],其中μ为整幅图像的均值,σ为整幅图像的平均差,直到找到使类间方差取最大值时的k值,即为最佳分割阈值th。

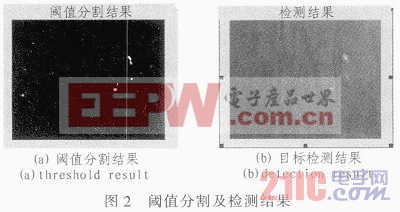

对经过Top-hat处理后的图像,利用上述的最大类间方差法获取阈值,利用这个阈值对图像进行分割,最后通过判断目标的形状大小,以达到提取目标的效果,如图2所示,图2(a)为阈值分割的结果,图2(b)为最终判断结果。本文引用地址:https://www.eepw.com.cn/article/150965.htm

2 硬件系统结构

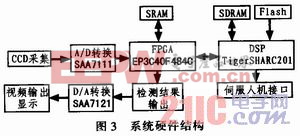

在实时视频处理系统中,底层算法的数据量大,运算结构相对比较简单,对速度有很高的要求,而高层处理算法控制结构复杂,数据量较底层算法少,故本文采用FPGA+DSP的结构。利用DSP实现目标检测的算法,可以提高运行速度及便于调试和修改,FPGA实现整个系统的控制和图像的基本预处理功能。整个系统的硬件结构如图3所示。

在系统设计中,DSP采用ADI公司通用浮点型TigerSHARC201,它拥有非常高的存储宽度,支持32位和扩展的40位浮点运算,支持8、16、32、64位定点运算。它拥有高达600 MHz的内核时钟速率,一个周期可以执行4条指令,相当于24次16 bit定点操作或者6次浮点操作。处理器的运算流水是双周期的,分支流水为2~6周期,鉴于此流水深度,它使用分支目标缓冲(BTB)来减少分支延迟,其两个相同的计算单元均支持浮点和定点运算。每周期最多可执行4个32-bit宽的指令,因此很容易实现高性能的应用。

FPGA采用Altera公司的EP3C40F484C对视频信号进行预处理和整个系统的时序控制,它具有多达24 624个逻辑单元,具有129个兼容的LV-DS通道,每个通道数据率高达640 Mb/s,还有4个可编程锁相环和8个全局时钟线。另外此芯片的功耗较低,全局运行时总功耗为300 mW左右。除此之外,FPGA作为系统的控制芯片还要为DSP及主机控制双口SRAM接口、外部存储器、视频编码器编码等单元提供准确的逻辑时序和可靠的驱动电路。

2.1 视频输入和输出模块

采用解码器SAA7111将摄像头输出的模拟视频信号转换为数字信号。SAA7111是飞利浦公司推出的9位视频解码器,提供6路模拟输入和2个增强型的模数转换器。通过配置SAA7111将PAL制式的模拟基带信号转化为CCIR-656格式的UYVY信号,并将其送入FPGA中,进行预处理。经过预处理后的图像数据再由FPGA重新打包成CCIR-656格式的数据送入到TS201的Link口。具体连接如图4所示,VPO[0…7]没有数据输入,VPO[8…15]是数据输出管脚与FPGA相连,时钟同步信号TS201采用MDMA的方式将原始图像信号存入SDRAM中,供目标检测算法使用。视频输出模块采用视频编码器SAA7121,标准的UYVY数据从FPGA的引脚输出,送到SAA7121的数据引脚,场、行同步信号分别接到FPGA的控制引脚上,通过行、场信号的控制,就能够输出显示正确的视频图像。在SAA7111和SAA7121工作之前,都需要对这两个芯片进行配置,它们的配置的参数都是通过FPGA产生I2C总线来实现的。

评论