嵌入式非易失性存储器在SoC物理设计中的应用

1.3 嵌入式NVM的选择

选择嵌入式NVM是一个综合衡量成本、功耗及性能的过程。因为嵌入式NVM通常会增加工艺步骤,使芯片制造的一次性成本和持续性成本都增加,同时,NVM的测试时间远大于芯片中的普通SRAM和ROM,因而增加了芯片的测试费用。因此,在选择NVM时,要从系统角度考虑以下几方面因素:

(1) NVM的用途。程序存储通常选用EEPROM或NOR flash,数据存储通常选用NANDflash;

(2) NVM容量。容量和面积、成本息息相关,小容量的NVM可以采用单位面积大但工艺更简单的特殊单层多晶工艺,而大容量的NVM则应采用面积紧凑的通用双层多晶工艺;

(3) NVM性能。通常需要考虑NVM的擦写时间、工作温度等参数;

(4)NVM的可靠性。可靠性主要有两个指标,即数据保存时间和数据擦写次数,若要较高的擦写次数,则EEPROM要优于flash。

2 嵌入式EEPROM

2.1 R36电力网远程抄表芯片简介

R36电力网远程抄表芯片是集成了模拟接口、m8051处理器、SRAM、ROM及EEPROM的SoC,其前身为外挂片外flash芯片的R35芯片,R36采用多晶片封装(Multi Chip Package,MCP),这种封装方案增加了芯片的制造成本,同时增加了系统的复杂程度,而且也降低系统的可靠性。而采用嵌入式EEPROM设计的R36将所有器件集成在一片芯片中,则使用普通封装即可,因而避免了上述问题。

R36采用SMIC 0.18μm EEPROM工艺,主要用来存储程序,故可依据需要选择SMIC 32KB及1KB的EEPROM IP各一个。该芯片已于2010年3月成功流片。

2.2 工艺映射

与普通logic工艺相比,SMIC EEPROM工艺需要多加9层掩膜和10次光刻,主要增加POLYl和ONO层,且其POLY2层与logic的POLY层在同一平面上,因此,在物理版图设计过程中,需要将EEPROM的POLY2层映射为POLY层,设计时可用通用的logic流程进行布局布线,并在生成最终GDSⅡ时,再将POLY层映射回POLY2,这样即可按EEPROM工艺流片。

2.3 布局布线

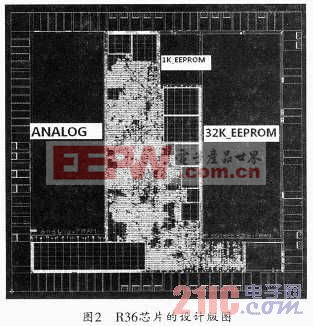

在芯片的布局阶段,需要仔细考虑EEPROM芯片的摆放位置。除了遵循一般嵌入式存储器摆放规则(尽量远离模拟模块)外,还需注意将EEPROM与其他电路之间留出足够隔离的空间(>5um),以防止噪声干扰;同时,所有EEPROM的摆放方向必须一致。在布线阶段,要给EEPROM提供充足的工作电源及稳定的参考电压,并禁止在EEPROM上层绕线以防噪声。图2所示是最终的芯片版图。本文引用地址:https://www.eepw.com.cn/article/150921.htm

3 结束语

嵌入式NVM以其数据可更改、掉电可保持、工艺可兼容等特点,已被越来越广泛地用于SoC物理设计中。相对于片外NVM方案,采用嵌入式NVM可以提高系统的稳定性及速度。然而,在设计过程中,都需要注意从用途、性能、容量及可靠性角度选择合适的嵌入式NVM解决方案,这样才能最终达到提高芯片性能、降低芯片成本的目的。本文给出了一个采用嵌入式EEPROM的电力网控制芯片R36的设计实例,同时分析了物理设计过程中需要注意的问题。结果证明,最终流片的芯片R36较采用片外flash的R35来说,成本降低不少,达到了设计目标。随着嵌入式NVM技术的持续发展,这款芯片也将采用更先进的NVM,并不断改进升级,以进一步提高性能、降低成本。

评论