嵌入式软件代码保护系统的设计方案

2.3 芯片内部EEPROM 存储数据内容介绍

由于存储器出自不同的厂商, 因此对于存储器的读写等命令存在着一定的差异, 为了满足系统对不同厂商芯片的适用性, 该代码保护芯片内部内嵌了一个64字节的可读写EEPROM, 用来存放一些特殊的数据,用户可以通过特殊的命令, 达到对相关地址的写操作。相关地址存放数据如下所示:

地址0x00至0x05: 分别代表SPI读操作指令代码、SPI写操作指令代码、SPI写状态寄存器指令代码、SPI读状态寄存器指令代码、SPI关闭写操作指令代码、SPI允许写操作指令代码。

地址0x06至0x07: 分别代表I2C 器件地址、I2C有效地址字节数。

地址0x08至0x0D: 分别代表NAND - Flash 读操作指令代码1、NAND - FLASH 读操作指令代码2、NAND - FLASH 读操作指令代码3 、NAND- FLASH 页编程操作指令代码1、NAND- FLASH 页编程操作指令代码2、NAND- FLASH有效地址字节数。

地址0x0E至0x25: 分别代表24字节的TDES密匙。

地址0x25以后的区域为保留区域, 预留给将来使用。

3.1 综合结果

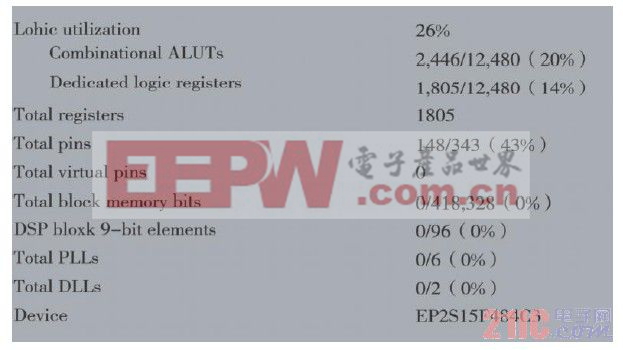

本文设计的嵌入式软件代码安全保护芯片, 使用V erilog 语言进行编程, 并进行了功能验证, 使用Quartus- 7 2进行了综合及布局布线, 并完成了后仿真。实验结果表明, 整个系统适用的时钟工作频率介于4MH z和96MH z之间, 满足目前主流的嵌入式系统的数据读写速度。使用Stratix II系列的EP2S15F484C3器件进行了综合, 综合结果见图4:

图4 综合结果

3.2 系统性能分析

3.2.1 基于I2C /SPI接口的存储器

当代码保护芯片第一次从处理器接收连续读操作指令后, 由于代码保护芯片需要从存储器预取64 字节, 所以必须等待1 28ms(和存储器通信的频率为400K) ; 因为代码保护芯片采取流水线技术的TDES, 所以第51个时钟周期后, 解密后的数据就可以传送回处理器, 由于在向处理器传送数据的同时, 代码保护芯片也同时从存储器接受数据, 因此, 处理器不需再等待额外的时间, 就可以连续的从代码保护芯片接受解密后的指令。因此当系统时钟工作频率为4MH z, 处理器必须等待1 29275ms后, 才可接收数据; 当系统始终工作频率为96MH z, 处理器只须等待1 28053m s后, 就可接收数据。

3.2.2 N and- Flash存储器

目前主流的Nand- F lash器件, 其最大的串行读出数据时间为50ns, 预取64 字节, 必须等待3200ns,TDES解密时间同节3.1.1, 因此当系统时钟工作频率为4MH z, 处理器必须等待15 95us后, 才可接收数据;而当系统时钟工作频率为96MH z, 处理器只须等待3 73125us后, 就可接收数据。

本文设计的嵌入式软件代码保护系统, 已经成功地对国家半导体公司的CAT1026芯片存储器进行解/加密读写操作, 虽然基于TDES的加密和解密的过程降低了嵌入式系统的运行速度, 但是以少量降低性能换取更高的产品安全性, 对于用户来说, 是完全可以接受的。它对于保护公司的知识产权、提高产品的市场寿命有着重要的、积极的意义, 有着极为广泛的应用前景。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论