嵌入式软件代码保护系统的设计方案

2. 1 内部结构简介

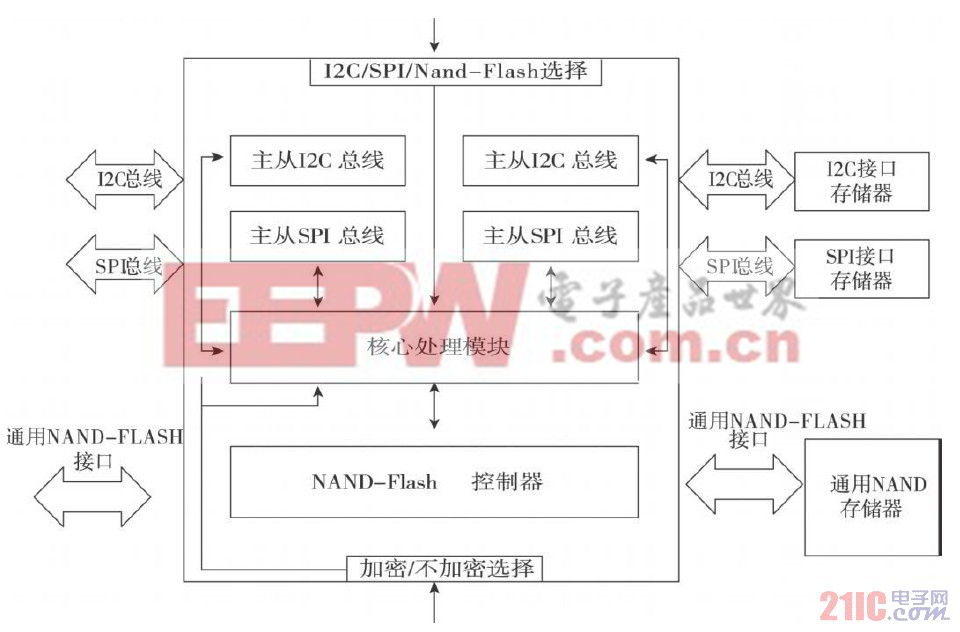

代码保护芯片隔断了原有嵌入式系统处理器和软件代码存储器之间的直接通路, 如图2所示。该系统主要分成主从I2C 总线接口模块、主从SPI总线接口模块、Nand- Flash通信模块以及核心控制模块。

如果用户选择I2C 接口, 芯片将通过I2C总线和存储器进行通信, 如果用户选择SPI接口, 芯片将通过SPI总线和存储器进行通信, 否则芯片将通过NAND- F lash模块和存储器进行通信。

如果用户选择加密模式, 那么处理器和存储器之间的通路将被隔断, 所有准备写入存储器的数据经过TDES加密后才写入其中, 所有从存储器读入的数据经过TDES解密后才送回至处理器执行; 如果用户选择不加密模式, 那么处理器将直接和存储器进行通信, 代码保护芯片将不启动任何加密/解密操作。这种设计方式, 使得芯片可以适用于更多的嵌入式系统, 同时也给予用户最大限度的灵活性。

图2 代码保护芯片架构

2 .2 核心处理模块

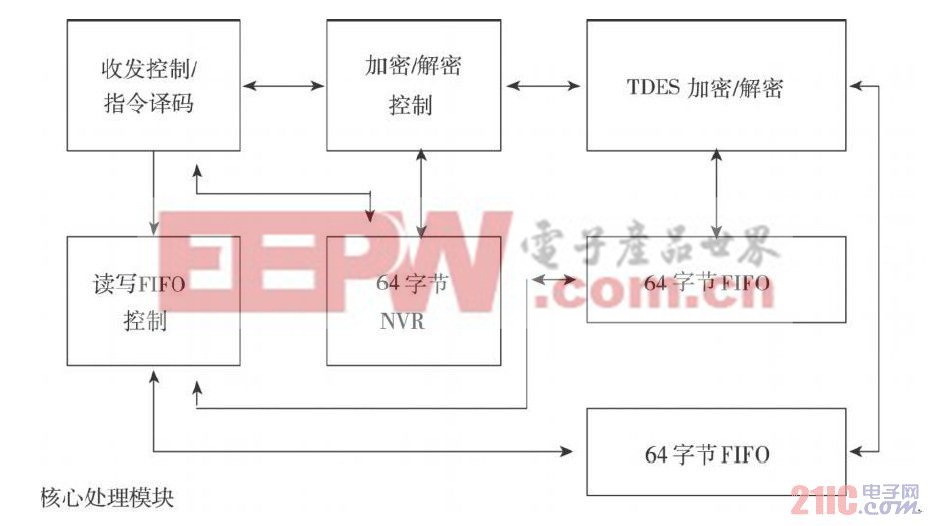

核心处理模块是整个系统的核心部分, 如图3所示: 主要完成指令译码、控制FIFO 的读写、控制TDES加密/解密的运行, 控制I2C、SPI、通用N and- Flash模块和外界的数据接收和传送以及对内部EEPROM进行操作。当代码保护芯片接收到处理器发出的读数据命令后, 将从存储器中预取64 字节的数据, 然后进行TDES解密。解密的同时, 芯片再次从存储器预取64字节的数据, 写入内部的另外的64字节FIFO 中: 乒乓FIFO 架构的设计以及采用流水线技术的TDES加密/解密, 大大提高了代码保护芯片的效率。

图3 核心处理模块框图

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论