Altera在FPGA中提供硬核浮点DSP,意义何在?

近日,Altera近日宣布在FPGA浮点DSP性能方面实现了变革,正在发售的Arria 10 FPGA在业界率先符合IEEE 754的硬核浮点DSP模块。未来,该硬核浮点技术也将集成在14 nm Stratix 10 FPGA和SoC中。

首席DSP产品规划经理Michael Parker在视频采访中表示,“这使Altera FPGA和SoC的性能和功耗效率比在更多的应用上优于微处理器和GPU。”可以满足大计算量应用需求,例如高性能计算 (HPC)、雷达、科学和医疗成像等。

DSP模块只占1/10 FPGA,性能相当于最优的DSP芯片

据悉,DSP模块只占FPGA的1/10左右。但是区区1/10的作用很大,Arria 10器件可实现1.5 TeraFLOP (每秒浮点运算次数)的DSP性能,“相当于性能最优的TI DSP”;而在未来的14nm Stratix 10器件中,DSP性能则高达10 TeraFLOP。

硬核浮点好在哪儿?

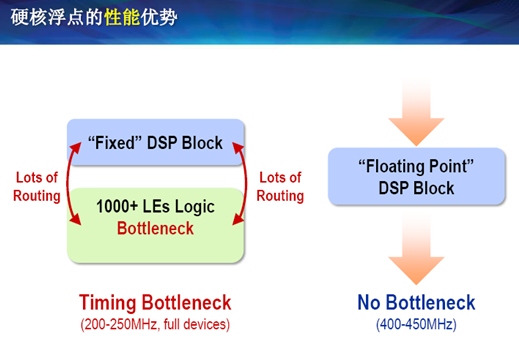

首先是性能提升。过去需要定点DSP模块和逻辑单元完成计算,之间需要大量布局,而Altera V系列主频只有200~250MHz。新的Arria 10的主频为400~450MHz,而且只需一个浮点DSP模块即可搞定。

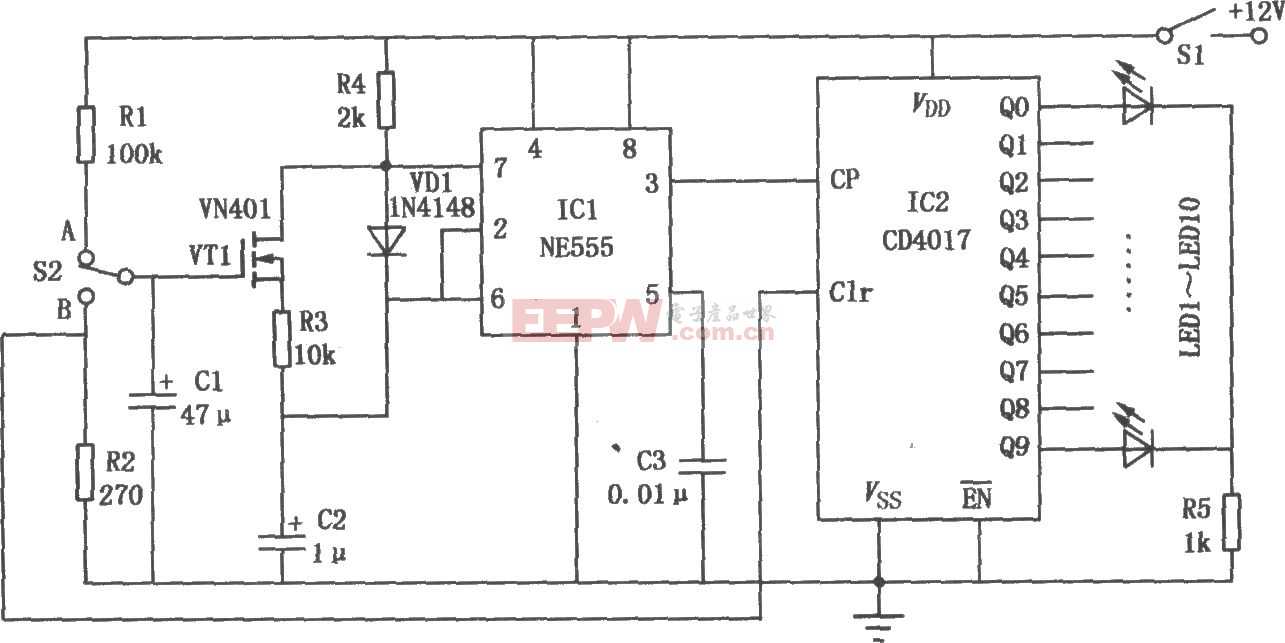

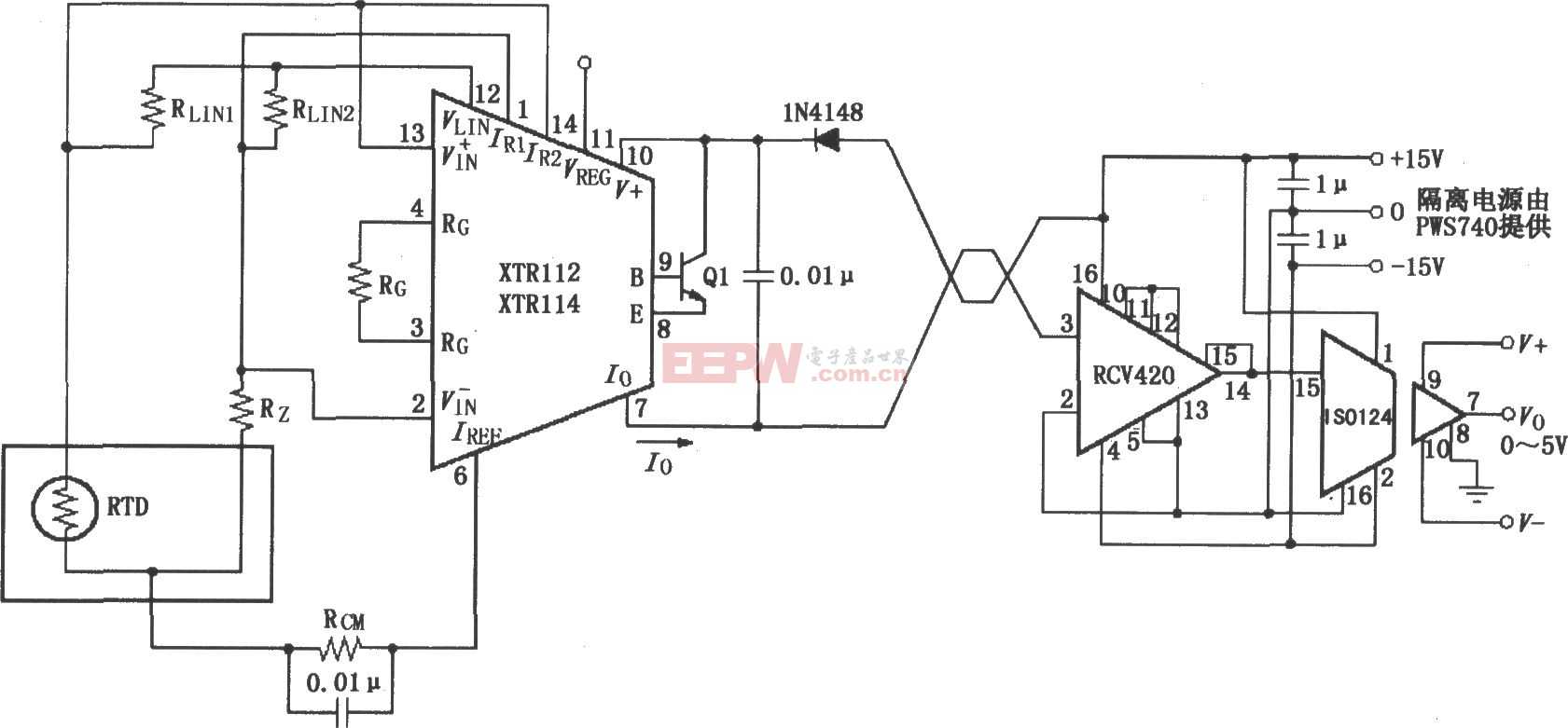

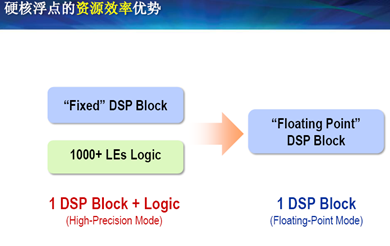

其次,硬核浮点的资源效率高。含在Arria 10和Stratix 10器件中的硬核单精度浮点DSP模块基于Altera创新的精度可调DSP体系结构。传统的方法使用定点乘法器和FPGA逻辑来实现浮点功能,而Altera的硬核浮点DSP与此不同,几乎不使用现有FPGA浮点计算所需要的逻辑资源(下图),因此,占1/10面积的DSP模块就可以把计算搞定。这不仅节约了资源,还降低了功耗。

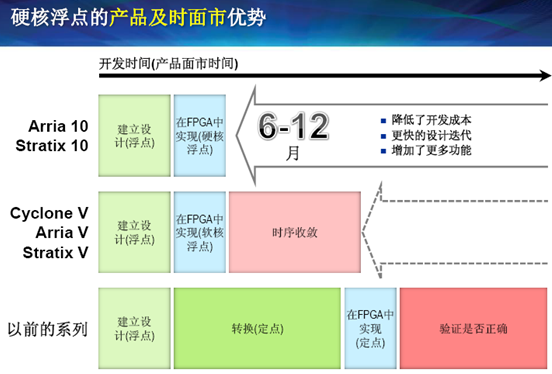

最后,开发时间也得到了简化。以前的DSP应用要经过建立设计(浮点),再人工转换成定点,在FPGA中实现定点,最后验证是否正确。而在Cyclone V等V系列中,Altera的工具采用了时序收敛等技术,使设计时间大大缩短。这一次,设计人员可以将其DSP设计直接转译成浮点硬件,而不是转换为定点。结果,大幅度缩短了时序收敛和验证时间。Altera还提供多种工具流程,帮助硬件设计人员、基于模型的设计人员以及软件编程人员在器件中轻松实现高性能浮点DSP模块。

“FPGA的每瓦性能最高”

FPGA具有精细粒度的密集流水线体系结构,因此非常适合用作高性能计算加速器。“在大计算量应用中,与DSP、CPU和GPU相比,FPGA的每瓦性能是最高的。”Altera公司软件和DSP产品市场经理Albert Chang指出。

意义

十多年前,FPGA做DSP,向独立DSP芯片发起挑战。现在Altera又在硬核浮点DSP模块方面有了新突破,无疑是FPGA取得的又一亮丽成就。

多年来,Altera十分重视高性能计算的小众领域,例如石油和天然气、数据安全、金融市场、研究、制造等,此次新产品推出,Altera用FPGA、DSP、ARM处理器等,继续捍卫在此领域的领先地位,并继续完成从FPGA向SoC的蜕变。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。