Synopsys推出Synphony高层次综合

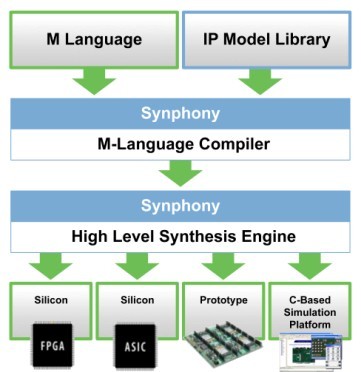

全球领先的半导体设计、验证和制造软件、硬件及知识产权(IP)供应商新思科技公司(NASDAQ: SNPS),今天宣布推出其Synphony HLS (High Level Synthesis)解决方案。该解决方案集成了M语言和基于模型的综合法,与 传统RTL流程相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。Synphony HLS为ASIC 和 FPGA的应用、架构和快速原型生成最优化的RTL。此外,通过在虚拟平台中为系统验证和早期软件开发生成C模型,Synphony HLS补充了基于C/C++的程序流。Synphony HLS与Synopsys的综合工具DC、Synplify Premier、Confirma、VCS、System Studio和Innovator产品一起,提供了从算法到最终芯片的最完整的原型、实施和验证流程。

本文引用地址:https://www.eepw.com.cn/article/98924.htm

Synphony HLS解决方案通过以下优点提供了比传统方式明显更高的效率:

- 从M语言到优化RTL的自动流程

- 针对ASIC和FPGA的架构优化生成RTL代码

- 用于早期算法验证的快速原型方法

- 生成C模型用于早期软件开发和快速系统验证

- 包括原型和ASIC应用在内的多个流程的统一验证

“Synphony HLS解决方案将显著地改变FPGA和ASIC在系统验证和嵌入式软件开发中的应用方式。” Toyon研究公司的算法开发师Richard Cagley博士说:“传统的HLS方法继续承担着重要的硬件工程资源,将我的算法翻译成RTL,在FPGA和ASIC芯片上进行运行。Synphony HLS使我能够用MATLAB®进行高层级仿真和产品编码,这意味着我现在仅用几小时或几天的时间就能够直接从仿真到达硬件,而不用数月或数年的时间。这对基于我们算法的生产力、生产进度和产品质量有广泛的影响。”

从M语言和高级IP到优化RTL的自动流程

由于Mathworks的MATLAB®环境能够在极高的抽象层级上进行简洁地行为表达,现已被广泛地用于算法探索和设计。在这种环境下开发的M语言模型通常在RT 层级 (RTL)下被进行重新编码和重新验证,有些情况下用C/C++进行实施和验证。与效率低下和容易出错的人工重新编码流程不同,Synphony HLS直接从高层次的M语言编码和Synphony HLS — 优化的IP模型库中创建可执行的RTL和C模型。通过采用独特的约束驱动的定点传播功能,设计师们可以快速和直观地从高层次浮点M码的可综合子集中获得定点模型。然后Synphony HLS引擎将合成已从架构上进行了优化的RTL,以满足面积、速度和功耗目标。Synphony HLS允许设计师们能够保留他们喜欢的算法建模语言,无需重新编码和重新验证模型,从而确保了早期的系统级别的验证和核查。

评论