DDR2器件HY5PS121621BFP在嵌入式系统中的应用

引言

本文引用地址:https://www.eepw.com.cn/article/88375.htmDDR2(Double Data Rate 2)SDRAM是由JED-EC开发的新生代内存技术标准,与上一代DDR内存技术标准相比,虽然采用时钟的上升/下降沿同时进行数据传输的基本方式,但DDR2内存却拥有2倍于上一代DDR内存预读取能力(即:4 bit数据读预取)。即就是,DDR2内存每时钟能以4倍的外部总线速度读/写数据,并且能以内部控制总线4倍的速度运行。

此外,由于DDR2标准规定所有DDR2内存均采用FBGA封装,而不是目前DDR广泛应用的TSOP/TSOP-II封装,FBGA封装可以提供良好的电气性能与散热性。DDR2内存采用1.8 V电压,可使功耗和发热量达到最低,此外,DDR2还具有OCD、ODT和Post CAS三项新技术。

OCD(Off-Chip Driver):离线驱动调整,DDR2通过OCD提高信号的完整性,通过调整上拉(pull-up)/下拉(pull-down)电阻使两者电压相等。使用OCD技术通过减少DQ-DQS的倾斜提高信号的完整性,通过控制电压提高信号品质。

ODT:内建核心的终结电阻器。使用DDRSDRAM的主板,为了防止数据线终端反射信号,需要大量的终结电阻。这样就大大增加了主板的成本。但实际上,不同内存模组对终结电路的要求是不一样的,终结电阻的大小决定了数据线的信号比和反射率,终结电阻小则数据线信号反射低,信噪比也低:终结电阻高,则数据线的信噪比高,信号反射也增加。因此主板上的终结电阻不能很好的匹配内存模组,甚至还会影响信号品质。DDR2根据自身特点内建合适的终结电阻,这样保证获得最佳的信号波形。使用DDR2不但降低了主板成本,还可获得最佳的信号品质,这是DDR无法比拟的。

Post CAS:为提高DDR2内存的利用效率而设定的。在Post CAS操作中,CAS信号(读写/命令)被插到RAS信号后面的一个时钟周期,CAS命令可在附加延迟(Additive Latency)之后保持有效。原来的tRCD(RAS到CAS和延迟)被AL(Additive Latency)取代,AL可以设置为0,1,2,3,4。由于CAS信号处于RAS信号之后的一个时钟周期,因此ACT和CAS信号永远不会产生碰撞冲突。总之,DDR2采用诸多新技术,改善了DDR的诸多不足。虽然DDR2具有成本高、延迟慢等诸多不足,但随着技术的提高和完善,上述问题终将得到解决。

2 HY5PS121621BFP简介

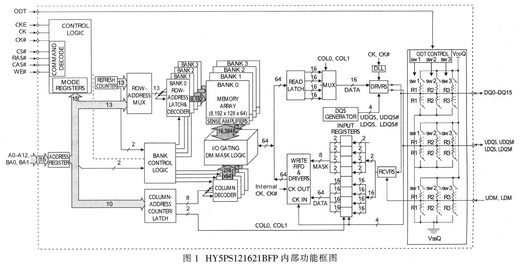

HY5PS121621BFP是Hyundai公司生产的一款512 MB DDR2器件,内部结构为32 M×16,工作电压为1.8 V,16位数据宽度采用84引脚FBGA封装。HY5PS121621BFP内部功能框图如图1所示,其引脚功能描述如表1所列。

3 应用实例

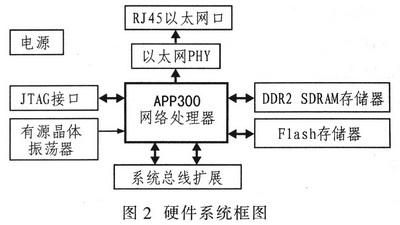

图2所示硬件系统的核心是一片Agere公司的APP300网络处理器,该网络处理器内嵌ARM 926E核,主频为133 MHz。APP300是Agere的Payload-Plus系列第四代网络处理器产品,片内集成有Clas-sifier、Traffic manager、Control processor等功能块,其处理能力为1.6 Gbit/s。APP320对外提供5个数据处理端口(Port0~Port4),可根据实际需要配置多种系统接口,支持不同的应用场合。APP300支持3种外部存储器接口,即200 MHz速率的DDR2SDRAM,支持内存的ECC保护功能:Program,DID,SED Parameter Memory(PP),Reassembly Packet BufferMemory (PK),ARM Processor Program/Data Memory(A P)。

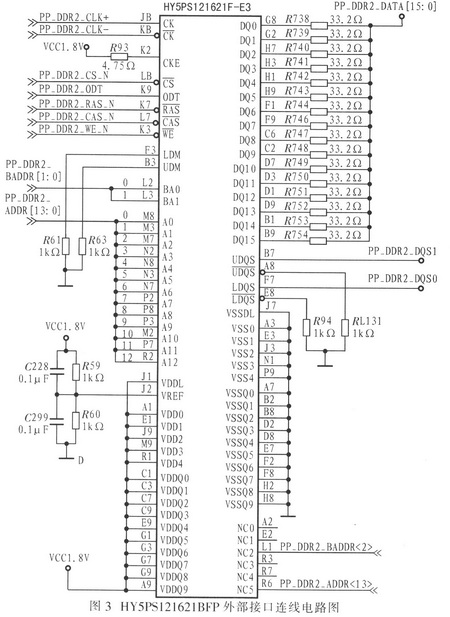

实际应用中,其内存配置为:PP(64MB×16 bit)、PK(64 MB×l6 bit)、AP(64MB×16 bit)。以AP内存为例,采用一片HY5PS121621BFP即可满足系统需要,详见图3所示的HY5PS121621 BFP外部接口连线电路图。数据总线串联33.2Ω的电阻(如图3所示)可避免过冲/下冲现象。由于HY5PS121621BFP的数据总线采用ODT技术内建核心的终结电阻器,所以其数据总线的末端不

用放置并联终端,但其地址/控制线没有采用ODT技术内建核心的终结电阻器,因此,应当始终在所有地址/控制线的末端采用并联终端,如图4所示。如没有适当的终端电压源,则可在VCCO电源端和接地端之间串联2只电阻器形成戴维宁等效终端电路。在这种情况下,只需要将地址/控制线的末端连接至包含这2只电阻器电路即可。

4 结束语

对于众多嵌入式应用,特别是那些需要大容量内存且高可靠性的系统,DDR2存储器是一种极佳的选择。虽然,嵌入式系统并不迫切需要提高内存速度,但目前DDR2取代SDRAM将成为主流。随着微处理器技术的发展,前端总线对内存带宽的要求越高,拥有更稳定的运行频率的DDR2内存将是大势所趋。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论