精密放大器和低噪声失调电路技术

1 运算放大器的现状

本文引用地址:https://www.eepw.com.cn/article/87786.htm运算放大器自1963年问世以来,走过了很长的发展道路,并成为所有线性系统中事实上的标准部件。几乎每个大型半导体制造商的产品线中都有运算放大器这个产品。根据不同的应用需求主要分化出通用型、低电压/低功耗型、高速型、高精度型四大类运放产品。目前放大器的性能水平已达到了如下指标,这在20世纪60年代是闻所未闻的:带宽超过1 GHz;转换速率超过5 000 V/μs;工作电流低于10μA;工作电压低至0.9 V;输入失调电压低于20 μV。

2 精密放大器

精密放大器一般指失调电压低于1 mV的运放,在使用过程中,他强调电路工作的低噪声和低失调性能。随着新型传感器技术(如导弹陀螺、MEMS微机械传感器等)的应用推广以及整机性能的提高,对该类型运算放大器的精度和带宽都提出了更高的要求。为了适应这种需求,国外IC公司已陆续推出了一些宽带产品。

3 低噪声失调电路技术

新型传感器的应用对运放精度提出了更高的要求,对微传感器来说,由于其输出信号主要处在低频端,且信号幅度很小,因此CMOS工艺带来的失调和低频1/f噪声的增加,对微传感器读出电路的设计提出了巨大的挑战。为了达到上一代CMOS工艺下相同的动态范围,电路需要尽可能保持最大的输出摆幅,以及采用各种技术降低失调电压和1/f噪声。

目前,主流的实现低失调、低噪声的电路技术主要有:自稳零AZ(autozero)技术、相关双采样CDS(CorrelatedDouble Sampling)技术和斩波稳零CHS(Chopper Stabilization)技术。本文主要介绍AZ和CHS技术。

3.1 自稳零技术(AZ)

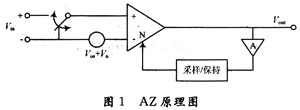

3.1.1 AZ基本原理

自稳零技术(AZ)的基本思想是,先将噪声和失调采样并保存,再将其从输入或输出的瞬态信号中除。当然也可以通过在输入和输出之间增加一个额外的端口来实现对噪声和失调的归零。如果噪声信号是不随时间变化信号(如DC失调),他将被消除;如果是一缓慢变化的低频随机噪(如1/f噪声),将被高通滤除。其原理如图1所示,假定输入参考失调电压为Vos,输入参考噪声为VN。AZ过程分为两个阶段:第一阶段,信号被隔离,AMP输入被短接,在采样脉冲的作用下,输入失调Vos和噪声VN被采样并保存,并以负反馈的形式从端口N引入,输出被控制在很小的幅度;第二阶段,信号接入,如果假定Vos和VN与采样时基本相同,那么噪声和失调将被消除。

3.1.2 AZ对噪声的影响

(1)对白噪声的影响

假定运放的等效输入白噪声等效为-3 dB带宽为fc的低通特性(LF)噪声,采样频率为fs,通常fc>>fs,AZ的输出白噪声可以近似为:

![]()

当fcTs=5时,白噪声在AZ过程前后的PSD可以清楚地从图2中看出,在奈奎斯特频率范围内(∣fTs∣≤0.5)折叠分量占主导地位。

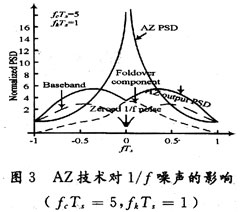

(2)对1/f噪声的影响

对于闪烁噪声(1/f)PSD我们可以通过相似的分析得到,设1/f噪声的转角频率为fk。如图3所示,由于采样函数在DC处引入了零点,1/f噪声被大大削弱。同时,虽然1/f噪声是一窄带过程,但其“尾巴”在采样过程中引入了混叠。在奈奎斯特频率范围内,1/f噪声混叠分量可以近似为:

![]()

3.1.3 存在的缺陷

AZ在消除运放失调的同时,也大大削弱了1/f噪声,但其欠采样过程引入了白噪声和闪烁噪声的频谱混叠,使得在信号频带范围内输出白噪声成份有所增加。同时,1/f噪声的“尾巴”也将在采样过程中导致输出的混叠,加大采样频率可减轻混叠,但与此同时也带来了负面效应,包括时钟溃通(clock feed-through)和沟道电荷注入(channel charge injection)效应。

电荷放大器相关文章:电荷放大器原理

评论