LPC2131基于CPLD的CAN接口设计

引 言

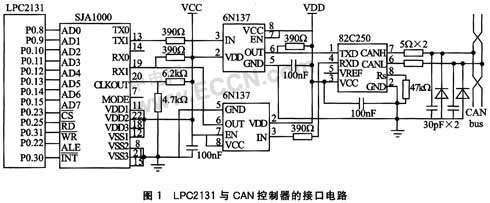

本文引用地址:https://www.eepw.com.cn/article/85165.htmPhilips公司的LPC213l是基于ARM7TDMI-S的高性能32位RISC微控制器。它具有ARM处理器的所有优点——低功耗、高性能和较为丰富的片上资源,但LPC2131内部没有集成CAN控制器,而无法利用CAN总线来进行通信。为了使得LPC2131能够利用CAN总线进行通信,可以通过外部扩展来实现其功能。目前,比较普通的方法是在LPC2131的外部采用CAN控制器设计CAN总线接口。LPC2131与CAN控制器的接口电路如图1所示。

这种方法中,LPC2131是通过GPIO口与CAN控制器SJA1000相连实现数据交互的。LPC2131通过寄存器IOSET/IOCLR来设定I/O口的高/低状态,虽然可以同时置位/拉低选定的引脚,但不能同时将某些口线拉高而将某些口线拉低。假定P0[15:8]初始状态为0xa5,若将P0[15:8]同时变为0x5a,则必须通过IO0SET和IO0CLR两次进行。程序实现如下:

PINSEL0=0x00000000;

IO0DIR=0x0000FF00;

IO0SET=0x5a00;

IO0CLR=0xa500;

P0[15:8]上会出现0xFF的中间状态。在高速通信系统中,这些中间状态可能会造成损失。虽然可以通过IO0PIN进行操作来消除这样的中间状态,但是Philips公司不推荐这种做法,非必要时尽量不要使用。

CAN驱动器接口芯片与LPC2131的串口接口电平上是相互匹配的,因此理论上可以将二者直接连接,采用串行通信方式实现。采用CAN总线通信,在长距离通信时,CAN总线两端要加终端电阻。其作用是避免数据传输又反射回来,产生反射波而使数据遭到破坏;同时,能提高总线传输的抗干扰能力。理论上,在每个接收数据信号的中点进行采样时,只要反射信号在开始采样时衰减到足够低就可以不考虑匹配。通常判断原则是根据数据速率和电缆长度进行匹配的,但这在实际中难以掌握,一般都是依据经验进行设计。

可编程逻辑器件(PLD)是20世纪70年代在ASIC设计的基础上发展起来的一种新型逻辑器件。20世纪80年代末,美国Altera和Xilinx公司分别推出大规模和超大规模的复杂可编程逻辑器件(CPLD)及现场可编程逻辑门阵列器件(FPGA)。自从进入20世纪90年代以来,可编程逻辑器件得到了飞速发展,向高度集成、高速度和低价位方向不断迈进;其应用领域不断扩大,可用于状态机、同步、译码、解码、计数、总线接口和串并转换等很多方面。使用CPLD可以提高系统集成度,降低噪声,增强系统可靠性并降低成本。

CPLD技术的出现,为我们提供了一种有效的解决办法:在CAN驱动器接口与LPC2131之间接一块CPLD,对CPLD进行功能编程,使其负责串行总线的数据传输和防止CAN发送反射。

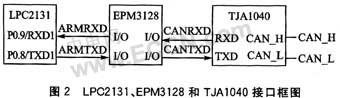

选择Altera公司MAX3000A系列的型号为EPM3128ATC100-7(简称“EPM3128”)的CPLD芯片。此芯片兼容3.3 V和5 V的I/O 口。这样,LPC2131、EPM3128和TJA1040在I/O电平上是相互匹配的。

1 EPM3128接口定义

EPM3128设置成双向串行总线通道。其中,2个I/O口被定义为CANRXD(IN)、CANTXD(OUT),分别连接CAN收发器TJA1040的RXD和TXD端,构成CAN总线上接收数据和发送数据通道;另外2个I/O口被定义为ARMRXD(IN)、ARMTXD(OUT),分别连接LPC2131的RXD1和TXD1端,构成处理器的串口接收数据和发送数据通道。整个数据的传输过程中,并不改变串行数据的协议和格式,接口电路全为TTL电平,期问不需要进行任何的处理。通信数据的校验、报错均交给通信两端的处理器完成。LPC2131、EPM3128和TJA1040的接口框图如图2所示。

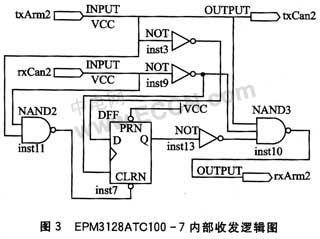

2 EPM3128功能实现

图3是采用功能块编程实现EPM3128的数据传输和屏蔽CAN发送反射的内部逻辑。图中txArm2、rxCan2定义为输入变量,分别对应外部的ARMTXD、CANRXD引脚;txCan2、rxArm2定义为输出变量,分别对应外部的CANTXD、ARMRXD引脚。总线空闲时,总线上的状态一直保持为“1”,即txArm2、rxCan2、txCan2、rxArm2的值全部为“1”。当输入总线收到一个状态“0”信号时,表示总线开始传输数据。如果LPC2131要发送数据,则LPC2131先向ARMTXD端口发送一个“0”起始信号,占据总线并在下一个时钟开始发送数据帧;如果TJA1040从现场接收到新数据,则TJA1040先向CANRXD端口发送一个“0”起始信号,占据总线并在下一个时钟开始发送数据帧。以此,完成正常通信过程中数据位从串口到串口的传输。

程序屏蔽CAN发送反射,就是屏蔽CAN总线接收到的从输出总线上反射的“0”信号,因为接口从高阻态被唤醒是靠一个“0”的起始信号。如果LPC2131正在发送数据,此时输人端口ARMTXD通过变量txArm2传送一位为“0”的信号到变量txCan2,并从输出口CANTXD送出。受总线辐射影响CANRXD输入口会从CAN总线接收到一个“0”信号,并将“0”信号传送给变量rxCan2,此时rXCan2收到的这个“0”信号是错误信号。经逻辑判断,程序将变量rxArm2维持为1,端口ARMRXD仍保持高阻态“1”。反射的“0”信号虽然被接收到,但在CPLD内部被屏蔽处理掉。如果没有屏蔽处理,那么这个错误的“0”信号将接收总线从高阻态唤醒,直接影响数据的通信。程序中D触发器的用途有两方面:一是缓存输入和输出,平滑信号的毛刺;二是实现控制信号的功能,如输出的复位和同步等。

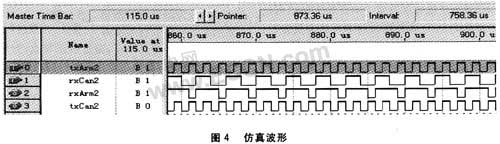

用QuartusII软件编译程序,并用仿真工具仿真。如图4所示,波特率为115 200 bps,编辑输入点txArm2、rxCan2的波形,查看输出点txCan2、rxArm2的波形。为方便识图,仿真中将数据端口传输占用的时间参数置0。

首先,论证输出波形的有效性。观察图4中的txCan2和rxArm2的波形,可以看出所有时刻的数值都是确定的,从而证明系统处于稳定状态,波形是有效的。

然后,论证输出波形的逻辑性。根据程序的逻辑设计,txArm2通道的数据发送享有优先权,始终保持txCan2=txArm2。从仿真结果可以看出,txCan2的波形与txArm2波形完全一致;当txArm2通道为“0”时,屏蔽rxCan2输入的数据,并保持rxArm2输出一直为“1”,观察图4中任何时刻所有输入/输出的波形,可以看出仿真结果正确。

最后,验证输出波形的时序性。这部分程序是一个组合逻辑的设计,也就是所有的输出随着相应的输入的变化而变化。由图4可知,仿真结果的时序正确。

结 语

本文基于CPLD技术实现了LPC2131与CAN总线之间的串行通信。该方法实现简单,并且稳定性较好,适合于采用CAN总线的多路串行通信系统。该技术已应用到实际中,接受实践的检验。

评论