基于fpga二维小波变换核的实时可重构电路

项目背景及可行性分析

本文引用地址:https://www.eepw.com.cn/article/266432.htm2.1 项目名称及摘要:

现场可编程门阵列为可进化设计提供了一个理想的模板。FPGAs 提供了一个硬件环境 ,这个环境 可将逻辑物理实现和 布线资源 按照为了特定功能所配置的比特流而重新组织构建起来。 RTR设计工具 绕过传统的fpga综合以及比特流生成过程 使可进化设计成为可能. JBits工具套装 就为在Xilinx 的Virtex系列和4000系列设备上進行RTR设计提供了一个设计环境。

这个项目旨在利用JBits实时可重构系统完成一个基于二维离散小波变换核的全面设计过程 ,这包括仿真 ,调试 ,以及搭建 硬件与可重构计算平台的接口。 JBits API的发展使对Xilinx 4000 系列和Virtex系列 器件配置比特流成为可能 。应用JBits API, 设计者可以绕开传统的逻辑综合和物理实现步骤 而允许高速比特流的重构。比较于asic 使用JBits 可以创造更高性能的电路以用于实时可重构系统 。因此 JBits API成为 设计一个有效的基于fpga的 实时可重构和可进化设计的必要工具。

2.2 应用背景

随着信息技术的飞速发展,计算机系统面临的问题越来越复杂,如何保证复杂系统的可靠性成为一个不容忽视的问题。可进化硬件给我们提供了一个很好的解决方案。可进化硬件EHW(Evolvable Hardware)是将进化算法和可编程逻辑元件融合在一起而产生的一种新的硬件研究流派。当所使用的环境发生变化时,或被放置于未知的环境中时,这种硬件会自动地改变内部结构,使之经常处于最适合状态,快速高效地完成规定的任务。

可编程门阵列(FPGA)以其独有的优点为国外多数研究人员用作硬件进化平台。EHW利用FPGA的在线可编程技术(ISP)及动态重构技术,将FPGA的配置信息作为染色体,通过遗传算法(GA)对其进行反复的适应度计算,交叉和变异,最终进化出符号环境要求的个体(即电路配置),从而使电路适合环境的变化。

与此同时,随着FPGA技术的发展,芯片的性能越来越强、规模越来越大、开发的周期越来越长,使得芯片设计业正面临一系列新的 问题:设计质量难以控制,设计成本也越来越高。IP(Intelligence Property)技术解决了当今芯片设计业所面临的难题。IP是指可用来生成ASIC和PLD的逻辑功能块,又称IP核(IP Core)或虚拟器件(VC)。设计者可以重复使用已经设计并经过验证的IP核,从而专注于整个系统的设计,提高设计的效率和正确性,降低成本。目前数字IP已得到了充分的发展,可以很方便地购买到IP核并整合到SoC的设计中。

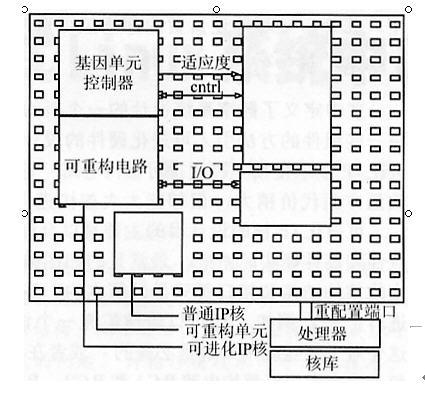

图 1 FPGA 中的 可进化ip核和 普通 ip核

因此,可以考虑将进化硬件的思想应用于IP核的设计中,设计一种可进化的IP核,根据当前的环境进化出相应的电路,并能够在普通的可重构器件中实现。

评论