基于fpga二维小波变换核的实时可重构电路

2.3 研究现状

本文引用地址:http://www.eepw.com.cn/article/266432.htm1 可进化IP核

从进化硬件的经验可知,系统通常只有一部分是适应性的(可进化的),另一部分可以通过传统的不可变的电路来实现。同样,使用IP核构造的系统也是有些IP核是可进化的,有些IP核是不可变的。可进化的那些IP核称为可进化组件或可进化IP核。

可进化IP核像普通的IP核一样被存储在组件库中,在被下载并放在一个可重构器件中后,它们将自动地进化它们的内部电路。当不再需要适应性行为时,可以从可重构器件中删除可进化IP核。可进化IP核和普通IP核的复用方式相同。

2 可进化IP核的一般体系结构

如图1所示,可进化IP核由可重构电路,基因单元和控制器构成(本文中可重构电路是指可进化IP核内的一个部分;可重构器件是指整个可重构平台,如FPGA)。这里要强调的是,基因单元不包含适应度计算,它只实现基因的操作、染色体存储和适应度存储。适应度的计算和环境由其它的核来提供。基因单元生成一些配置并上载到可重构电路中去,环境对这些配置进行评估,并将适应度值发送给IP核。可进化IP核实际上是一个由环境控制的电路生成器。

环境(由其它核提出)和可进化IP核之间的通信如下:首先IP核被初始化(生成初始化种群),然后进入如下无限循环——当环境发生变化后,环境计算当前电路配置的适应度,并判断电路是否适应环境。如果染色体存储器中的配置不可用,则向IP核发出控制信息,IP核开始进化。即基因单元把硬件配置信息作为染色体,根据适应度对其进行交叉、变异等遗传操作,生成一个新的种群。环境对新种群进行适应度计算,并判断是否有满足当前环境的个体(配置)。若没有,向IP核发控制信息,遗传单元继续对电路配置进行进化,直至有满足当前环境的配置为止;若有,则将适应度值发给IP核,IP核用这个新生成的最优配置来重配置可重构电路,并在染色体存储器中保存当前最优配置及其适应度值,等待来自环境的下一个请求。

环境总是要求下载当前最优的进化电路,因此,IP核必须保存目前为止最优的配置,并且在需要的时候提供出去。可进化IP核总是屏蔽重构过程,因此它对于外部环境来说是不可见的。

对于一些特殊的应用,必须为它们开发专用的可进化IP核,因为反映应用的要求基因单元和可重构电路的体系结构将使进化过程优于一个随机的搜索。由于适应度计算是在IP核外进行的,因此IP核原则上支持动态适应度函数和无限的进化。可进化IP核可以用软件实现。

三 项目实施方案

3.1方案基本功能框图

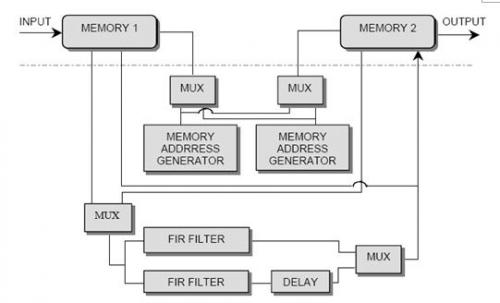

图2 系统框图

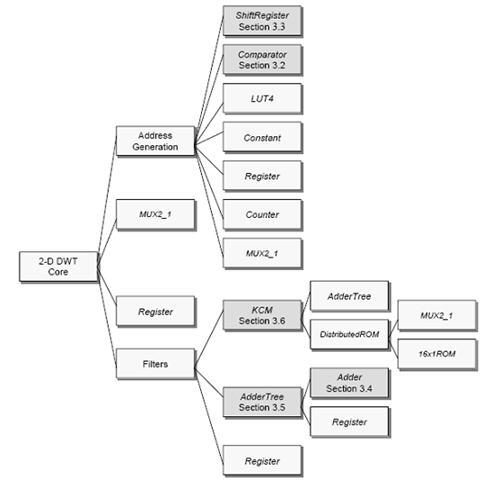

图3 DWT2D核原理图

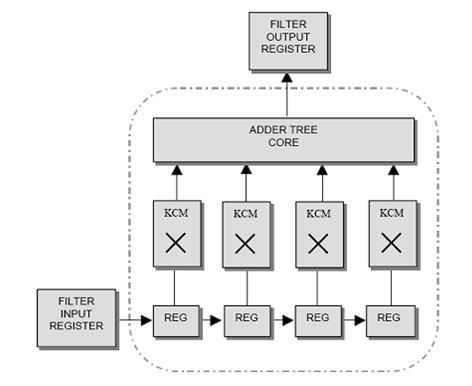

图 4 由四个RTP核构成的四拍FIR滤波器

评论