基于fpga二维小波变换核的实时可重构电路

1.硬件部分

本文引用地址:http://www.eepw.com.cn/article/266432.htm可进化IP核的实现

3.1 实现中的问题

可复用的IP核通常有软核、固核和硬核三种。本文讨论的是软核。本文的目标是,设计和实现以HDL源代码(例如,VHDL)表示的可进化IP核。其优点是IP核的表示独立于平台,这样它们就可以在各种不同的目标结构中运行。要解决的主要问题是,可进化的IP核的内部可重构电路的自动重构(因为它们是可进化的)。

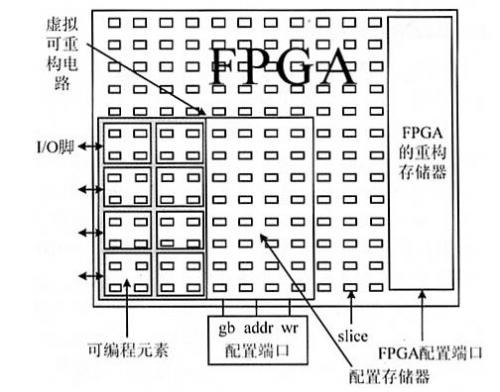

图 5 用vertex slice 实现的虚拟可重构电路

当一个可进化IP核从一个组件库中被下载到可重构器件的一个指定位置时,它的内部可重构电路必须进行重构。这就意味着这个可重构器件中的一些可编程块必须能配置这个可重构器件的其它内部可编程块。另外,这个可进化IP核(它的基因单元)能被放置于这个可编程阵列(即可重构器件)的任何位置,也就是说,这个可重构器件中必须支持内部重构。

FPGA以其动态可重构的优点,无疑是可进化IP核的最佳实现平台。然而,通常的FPGA并不支持内部重构,而只允许通过一个特殊的配置接口外部重构(如图5)。目前,只存在一种支持内部重构的平台,就是单元阵列,但这种芯片目前还相当少。因此,为了在普通FPGA器件实现可进化IP核,使之能在实际应用中发挥作用,必须采用其它的一些方法。硬件虚拟化是基于FPGA的系统常用的一种设计技术。从这个思想出发,本文采用了一个被称为虚拟可重构电路的技术来实现可进化硬件中的内部可重构电路。但文中对设计虚拟可重构电路的概念进行了扩展。

3.2 虚拟可重构电路

一些FPGA芯片支持部分重构,也就是允许可重构系统的一部分重构,而不影响其余部分的运行。部分重构的优点在于,其重构所花的时间比全部重构更少。本文以支持部分重构的Xilinx Virtex FPGA为例,来说明虚拟可重构电路的实现。IP核可以动态地下载到FPGA或从FPGA删除。所有的操作都通过Virtex重构端口和Jbits接口来完成。当一个可进化IP核被下载时,它的重构位串在指定位置构靠下列单元;虚拟可重构电路、基因单元和控制器。

图5表明,虚拟可重构电路实际上是一种在普通FPGA上实现的新的可重构电路。本例中由八个可编程元素构成,由Virtex单元(slice)实现。Virtex单元实现新的可编程元素阵列、新的布线电路和新的配置存储器。虚拟电路能内部重构,但如果有其它新的配置存储器与之连接,也可从FPGA的I/O引脚配置。

这种方法的优点在于:可根据具体的应用需要准确地设计可编程元素阵列、布线电路和配置存储器。虚拟可重构电路的重构方式和粒度能准确地反映具体应用的需要。通过虚拟可重构电路,很容易把领域知识插入到基因单元和可重构电路的体系结构中,从而获得电路软件模型的精确实现。

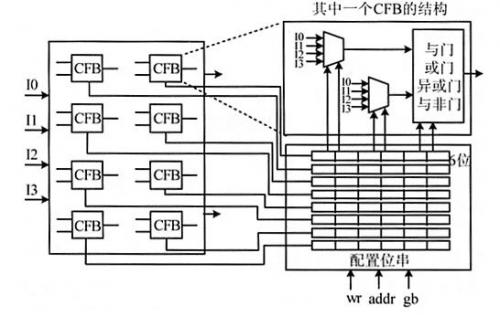

图6给出了一个虚拟可编程元素的例子。这个虚拟可重构电路由8个这样的元素构成,有4个输入和2个输出。这些虚拟可编程元素称为可重配置功能块CFB(Configurable Functional Blocks)。每个CFB对应一个配置位串(这里的位串为6位),其中两个配置位决定了CFB的功能,其它四位定义了输入的连接信息。布线电路由多路器组成,它们由配置存储器中的位串控制。配置存储器由Virtex单元构成,一个Virtex单元包含两个触发器,用于存储配置位串中的两位。配置存储器的所有位都连到多路器,多路器控制布线和CFB中功能的选择。

虚拟可重构电路中CFB的数量由具体的应用决定。虚拟可重构电路用结构级VHDL语言来描述,但是一些基本的电路(例如“MAX”电路)用行为级来描述。虚拟可重构能在不同的目标器件下综合,目标器件并不需要支持部分重构。

图 6 虚拟可重构电路及其中一个CFB的实现

3.3 基因单元和控制器

基因单元和控制器的实现通常有两种选择:采用普通微处理器实现,或者设计一个专用的电路来实现。

专用的电路是指一种进化算法的硬件实现,目前在可进化硬件领域已经开发了很多这样的实现。这种算法的优点是电路的进化速度快,适合于复杂的应用。

采用微处理器实现时,可以购买或免费获得现成的微处理器软核,如Xilinx提供的MicroBlaze和PicoBlaze微控制器IP核,Altera生产Nios核,等等。此外,如果给出的目标可重构器件中有片上处理器,可以使用片上处理器,Xilinx Virtex II Pro XC2VP50芯片包含四个PowerPC处理器。处理器必须通过编程来执行程序,它们能和核周围的环境进行通信并完成对染色体的基因操作。此外,处理器还负责内部虚拟可重构电路的重构。

评论