Arm是全球知名芯片架构企业,也是知名芯片IP核供应商。大部分IP核都可以直接向IP厂商采购获得,再由芯片设计企业在此基础上设计出自己的芯片。高通和华为即在Cortex-A系列处理器的基础上,设计出骁龙和麒麟芯片。就是这家知名的企业在近期迎来一波大裁员,据媒体报道,Arm中国从上周开始裁员,主要裁减研发团队, 其中SoC、HPC两个团队裁撤人数最多,其余的研发团队会有不同程度的小范围裁减,赔偿比例N+3。当前,Arm中国人员1000人左右,研发人员在700人规模, 研发产品覆盖:SOC

关键字:

ARM中国 芯片架构 IP核 SOC 裁员

重点:高质量DesignWare DDR PHY IP核为NVIDIA提供无与伦比的性能、延迟和电源效率DDR PHY支持DDR5/4的每个通道多个DIMM,满足NVIDIA的网络数据速率和内存容量要求基于固件的现场可升级训练可提高通道的稳定性和可靠性,并且有助于算法更新,从而降低采用新内存协议的风险新思科技(Synopsys, Inc.)近日宣布,NVIDIA的网络业务部门Mellanox将采用经验证的DesignWare® DDR5/4 PHY IP核,以满足其针对高性能计算和人工智能应用的Infin

关键字:

云计算 NVIDIA 新思科技 DesignWare DDR IP核

本项目实现了一种基于CM3内核的SoC,并且利用该SoC实现网络数据获取、温度传感器数据获取及数据显示等功能。在Keil上进行软件开发,通过ST-LINK/V2调试器进行调试,调试过程系统运行正常。在Quartus-II上进行Verilog HDL的硬件开发设计,并进行IP核的集成,最后将生成的二进制文件下载到FPGA开发平台。该系统使用AHB总线将CM3内核与片内存储器和GPIO进行连接,使用APB总线连接UART、定时器、看门狗等外设。

关键字:

FPGA IP核 Cortex-M3 SoC 201902

HiFi 5 DSP将基于神经网络的语音识别算法性能提高达4倍楷登电子(美国Cadence公司,NASDAQ:CDNS)今日发布面向音频和语音处理的Cadence® Tensilica®HiFi 5 DSP,是首款为高性能远场处理和人工智能语音识别处理量身优化的IP核。对比HiFi 4 DSP,第五代HiFi DSP的音频处理性能提高2倍,神经网络(NN)处理性能提高4倍,是数字家庭助手和车载娱乐系统语音控制用户界面的理想选择。随着数字家庭助手普及度的快速上升,语音控制用户界面已经成为厂商开发创新消费产品

关键字:

HiFi 5 IP核

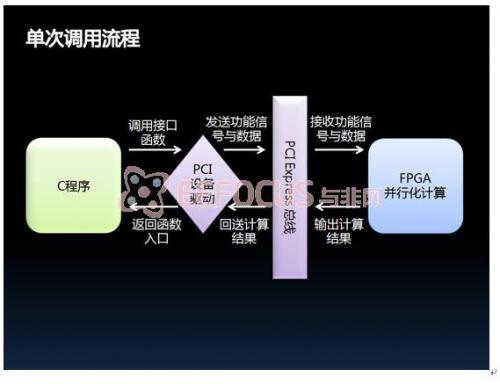

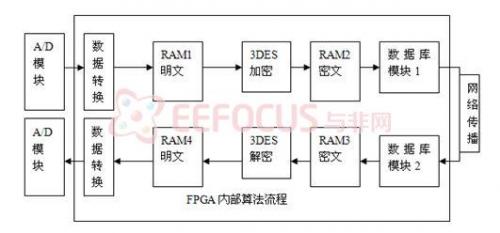

现代测控系统和通信领域对数据传输速率的要求越来越高。相比PC 中其他技术的发展,总线技术的发展显得相对缓慢,总线性能已经成为制约系统性能发挥的

关键字:

现场可编程门阵列 DMA控制器 IP核

IP(Intelligent Property)核是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的

关键字:

FPGA IP核 固核概念

基于NiosII 软核的SOPC(System ON Programmable Chip)是Altera 公司提出的片上可编程系统解决方案,它将CPU、存储器、I/O接口、DSP 模块以及锁相环(P

关键字:

Avalon总线 LCD控制器 IP核

GPIB控制器软件的IP核设计方案详解-随着网络技术与通信技术的高速发展,测试仪器和测试技术发生了革命性变化,“网络就是仪器”确切地概括了测试仪器间的网络化发展趋势。

关键字:

IP核 GPIB

一种新型的LCD驱动电路IP核的总体设计-本文介绍了LCD的通用驱动电路IP核设计,采用自顶向下的设计方法将其划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性,可驱动不同规模的LCD电路。

关键字:

IP核 驱动电路 LCD

FPGA实战开发技巧(13)-基于IP的设计已成为目前FPGA设计的主流方法之一,本章首先给出IP的定义,然后以FFT IP核为例,介绍赛灵思IP核的应用。

关键字:

FPGA 赛灵思 IP核

对现有主要IP核保护方法的原理和性能进行了研究分析,指出了各种方法的优缺点,同时指出了IP核保护方法的发展方向。 随着集成电路的规模依据摩尔定律不断呈指数增长,目前已经可以将整个系统集成到一块单硅芯片上,片上系统(Sys-tem on a Chip, SoC)的概念也应运而生。然而对于大型的SoC 来说,无论从设计的费用、周期还是可靠性来考虑,传统的设计方法均已不能满足需求,因此,基于知识产权( Intellectual Pro-perty, IP)核复用的设计方法也就随之出现。

关键字:

片上系统 知识产权核 数字水印 签名 IP核

对于利用LabVIEW FPGA实现RIO目标平台上的定制硬件的工程师与开发人员,他们可以很容易地利用所推荐的组件设计构建适合其应用的、可复用且可扩展的代码模块。基于已经验证的设计进行代码模块开发,将使现有IP在未来应用中得到更好的复用,也可以使在不同开发人员和内部组织之间进行共享和交换的代码更好服用。

关键字:

LabVIEW 代码模块 FPGA IP核

NGN作为一个面向未来网络业务应用,基于分组平台可以同时提供语音、数据、多媒体等综合业务的系统,成为各大运营商以及设备提供商关注的焦点。 在影响NGN运营模式和运营收益的各种关键因素中,IPQoS特别是核心网的IPQoS,无疑是非常重要的一项。

关键字:

IP核

ip核介绍

IP核概述

IP核则是一段具有特定电路功能的硬件描述语言程序,该程序与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片。利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP核的市场活动还不规范,但是仍有许多集成电路设计公司从事IP核的设计、开发和营销工作。IP核有两种,与工艺无关的VHDL程序称为软核;具有特定电路 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473