亚微米CMOS电路中VDD-VSSESD保护结构设计一

1 引言

ESD(Electric Static Discharge)保护结构的有效设计是CMOS集成电路可靠性设计的重要任务之一,其ESD结构与工艺技术、特征尺寸密切相关,随着IC工艺技术的进一步发展,特征尺寸越来越小,管子的栅氧层厚度越来越薄,芯片的面积规模越来越大,而外围的使用环境并未改变,因此ESD的失效问题面临越来越严峻的考验,在亚微米CMOS IC中,通常做LDD(Lightly-Doped Drain)注入,在深亚微米超大规模CMOS IC设计中,通常有Silicide 或Salicide技术,这些技术的使用有助于提高电路的速度、集成度、可靠性等,但这些技术对电路的抗ESD性能极为不利,降低了ESD可靠度。在亚微米以下的电路设计中,需要对电路进行全芯片的ESD保护结构的设计。如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为全芯片设计者的主要考虑的问题。

2 电路实例

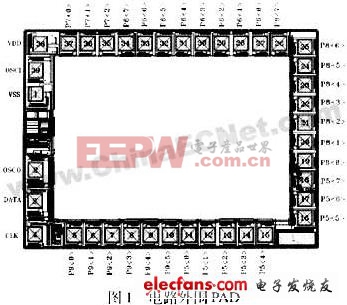

电路为键盘编码控制电路,采用0.5μm-0.6μm SPSM CMOS阱工艺,工作电压为3V、5V,除ROM外集成度约5000门,面积为2.0×1.5mm2,一共有39个PAD,其中I/O引脚36个,一个时钟振荡输入脚,一个VDD,一个VSS。PAD排列如图1所示。

I/O口的保护结构为Finger型MOS输出管及GGNMOS管,VDD与VSSPAD旁边各有一个VDD-VSS电压钳位保护电路,逻辑结构如图2。该结构在电路正常上电工作时,N1管作为一个VDD与VSS之间的反向二极管,而在ESD发生时,N1管开启,作为ESD瞬时低阻抗大电流泄放通道,VDD与VSS之间的电压则被钳位,从而起到保护内部电路的作用。该结构又称为ESD瞬态检测电压电路,其中R是由N阱电阻构成,C为MOS电容。

用ESD模型之一的人体模型工业测试标准HBMMIL-STD-883C method 3015.7对其进行ESD打击实验。

结果在I/O-VDD、I/O-VSS、I/O-I/O模式下,其抗击电压可达到4kV以上,但在VDD-VSS模式下,只能达到750V,在1kV时,电源与地短路从而造成整个电路失效。

初步分析的结果为,电源与地之间的保护结构如图2,在版图的设计上有薄弱环节,使该结构自身的健壮性级差,从而影响了整个电路的ESD性能。

为了验证这一想法并找到改进的办法,对该电路做了下述实验。

首先,对电路做液晶分析实验,即在电路上滴上几滴特殊的化学物质(具有流动性),然后在VDD与VSS的管脚灌入大电流,该化学液体聚集在VDD与VSS通路上电流最集中处,从而找到了击穿点。该击穿点就在VDDPAD附近,见图3中画圈的地方。

评论