新一代0.30毫米间距芯片级封装(CSP)面临的组装和设计挑战

引言

本文引用地址:https://www.eepw.com.cn/article/203217.htm由于手持设备永无止境的小型化和需要更先进的功能,应对小型化的能力对于满足这些要求至关重要。小型化可以通过多种方式实现,而本文将探讨0.30毫米间距的芯片级封装。关键是确保组装的几个选择可以实现,并且应被看作技术工具盒。封装内有源元件的裸片堆叠是提高印刷电路板组装(PCBA)每个单元区功能的一种方式。但是,创建堆叠的裸片解决方案存在一些缺点。

首先,这个方法是一个定制解决方案。如果任何用到的裸片发生变化,则需要评估裸片堆叠以确定封装是否需要改变,例如,裸片缩小可能改变整个封装的结构。第二,如果封装内的一个或多个裸片出现故障,整个单元必须废弃,这会导致成本增加,这就是著名的“复合良率”问题。最后,协调多家半导体供应商为封装厂提供裸片以进行裸片堆叠也是极具挑战性的任务。

堆叠封装(PiP)是提高印刷电路板组装(PCBA)每个单元区功能的另外一种方式。PiP类似于裸片堆叠,但不是堆叠裸片,而是基带封装和内存封装等完整的封装进行堆叠并放入模具。这让内存能够在堆叠之前进行全面测试,但通常封装成本高于堆叠裸片或PoP配置。

在PoP流程中,一个元件在单SMT流程中放到另外一个封装上,以便全面利用产品的三个维度。底部元件的顶端的焊盘类似于印刷电路板上方用于连接顶端封装的焊盘,每个封装是一个单元,可以作为目前常规的集成电路封装进行全面测试,其良品率与目前常见的良品率相当。堆叠的封装可以在传统SMT环境中处理,包含几个立即可用的升级。因此,封装堆叠实现了可配置的组件,并在供应链中带来更高的灵活性。它可用于内存应用或包含内存的处理器,加快上市时间并更好地管理封装测试和复合良率问题。

缩小间距无疑是有源元件最重大的挑战之一,但这是实现小型化非常有效的方式。目前的主流是0.4-0.5毫米间距,0.3毫米间距正在到来。从0.5毫米到0.4毫米主要给设计、丝网印刷以及印刷电路板的质量带来了多个挑战。对于0.3毫米间距,有很多问题需要在投产前予以解决。两个关键问题是确定是否适用丝网印刷或焊液/焊膏浸渍以及是否需要氮气或更好的东西。

测试台与材料

本研究中的测试台类似于手机,但基于有关外部尺寸的IPC跌落测试台JESD22-B111。面板尺寸为132mmx77mm(图1),由三个完全相同的部分组成。该电路板的表面涂层是有机表面防腐剂(OSP),印刷电路板的一侧使用了阻焊层限定(SMD)焊盘,而另一侧使用非阻焊层限定(NSMD)焊盘。

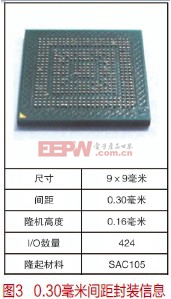

用作测试台的印刷电路板有四层,在外层使用无卤素附树脂铜皮(RCC)以实现更高质量的微孔,内层使用无卤素FR4,整个印刷电路板的厚度是0.788毫米。由于铜焊盘很小,非阻焊层限定为0.20毫米而阻焊层限定为0.25毫米——而且需要很小的微孔,我们决定使用铜填充的微孔。

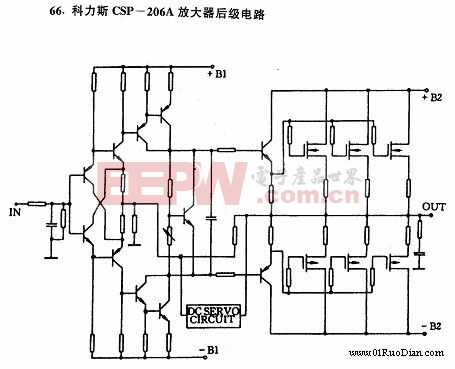

在之前对0.40毫米间距CSP的研究中,我们看到丝网印刷效果更好,因为焊膏有更大的粘贴面积,而所谓的微孔带来的空间或多或少地消失在CSP和BGA隆起的连接处(图2)。0.30毫米间距CSP元件(图3)是菊链形式,涵盖所有焊点。

焊膏选择

我们的所有研究均使用4型SAC 305(Sn96.5Ag3Cu0.5)无卤素焊膏,是广泛地评估了印刷能力、间隙、隆起、焊点、浸润和SIR(表面绝缘电阻)之后做出的。

pic相关文章:pic是什么

回流焊相关文章:回流焊原理 绝缘电阻测试仪相关文章:绝缘电阻测试仪原理

评论