2024年,存储新技术DDR、HBM等大放异彩!

迈过2023年的经济逆风行业下行周期,2024年存储市场起势,存储芯片价格上涨。为了适配近两年人工智能热浪需求,存储新技术革新步伐加速,DDR、LPDDR、GDDR新技术在2024年迎来放量周期;HBM加速迈进,HBM3/HBM3e持续突破,有望带动存储市场迸发新的活力。

本文引用地址:http://www.eepw.com.cn/article/202403/456376.htm一

2024是DRAM技术迸发活力的一年

从1998年三星生产出最早的商用DDR SDRAM芯片,到DDR1、DDR2、DDR3、DDR4的延续,再到今年跃升主流的DDR5,和即将到来的DDR6、DDR7,DRAM技术还在持续突破。按照不同的应用场景划分,固态技术协会(JEDEC)把DRAM分成标准DDR、LPDDR、GDDR三类,其中DDR主要应用于服务器和PC端,LPDDR主要应用于手机端和消费电子,GDDR的主要应用领域为图像处理领域,近期上述三类DRAM技术新品对原厂营收占比贡献不断上升。

2024年是DDR5/LPDDR5的天下

在主流DRAM市场格局上,三星、美光、SK海力士三分天下,目前DDR5/LPDDR5市场竞争。

以上述三家为主流。此外,中国台湾存储企业华邦及南亚科技,以及大陆存储企业长鑫存储的定位也在主流DRAM市场。

从过往历史看,每代DDR新标准发布后都需要经过2年左右的优化,才能实现性能的较为全面的稳定提升,而后实现对上一代产品的市场替代则可能需要3到5年的时间。业界数据显示,DDR3和DDR4都享有大约7年的生命周期。DDR4存储器标准于2012年发布,而其初代产品则于2014年入市,直到2016年才实现了市场份额的大幅提升。

对于最新一代的DDR5而言,经历了2023年上半年的产能爬坡和性能攀升,下半年在三大原厂营收比重不断上升,并在2024年正式迎来黄金发展期。

据TrendForce集邦咨询研究显示,2023年四季度三星(Samsung)营收高达79.5亿美元,季增幅度逾五成,主要受惠于1alpha nm DDR5出货拉升,使得Server DRAM的出货位元季增超过60%。SK海力士(SK hynix),虽然出货位元季增仅1~3%,然持续受惠于HBM、DDR5的价格优势,以及来自于高容量Server DRAM模组的获利,平均销售单价季增17~19%,第四季营收达55.6亿美元,季增20.2%。美光(Micron)量价齐扬,出货位元及平均销售单价均季增4~6%,DDR5与HBM比重相对低,故营收成长幅度较为和缓,第四季营收达33.5亿美元,季增8.9%。

而LPDDR5方面,TrendForce集邦咨询认为,AI PC有望带动PC平均搭载容量提升,并拉高PC DRAM的LPDDR比重。以Microsoft定义的满足NPU 40 TOPS的CPU而言,共有三款且依据出货时间先后分别为Qualcomm Snapdragon X Elite、AMD Strix Point及Intel Lunar Lake。其中,三款CPU的共同点为皆采用LPDDR5x,而非现在主流采用的DDR SO-DIMM模组,主要考量在于传输速度的提升;以DDR5规格而言,目前速度为4800-5600Mbps,而LPDDR5x则是落于7500-8533Mbps,对于需要接受更多语言指令,及缩短反应速度的AI PC将有所帮助。因此,TrendForce集邦咨询预期,今年LPDDR占PC DRAM需求约30~35%,未来将受到AI PC的CPU厂商的规格支援,从而拉高LPDDR导入比重再提升。

行业人士表示,由于DDR5/LPDDR5(X)技术愈发成熟,其保质期或将比上一代更长。目前,存储厂商目前扩产重点集中在HBM、DDR5与LPDDR5(X)产品上。

TrendForce集邦咨询研究显示,产能规划方面,三星去年第四季大幅减产,在库存压力改善后,今年第一季投片开始回升,稼动率约为80%。下半年旺季,需求预期将较上半年明显增温,产能会持续拉高至第四季。SK海力士则积极扩张HBM产能,投片量缓步增加,随着HBM3e量产后,相关先进制程投片亦持续上升。美光投片量有回温趋势,后续将积极增加其先进制程1beta nm比重,用于生产HBM、DDR5与LPDDR5(X)产品,因先进制程的设备增加,届时产能将较为收敛。

GDDR7显存标准正式发布

3月6日,JEDEC(固态技术协会)正式发布了GDDR7显卡(JES239图形双倍数据速率(GDDR7)SGRAM)技术规范,旨在提供更高的带宽、更高的数据传输速率、更高的能效和更大的存储容量,以支持未来高性能计算应用的发展。

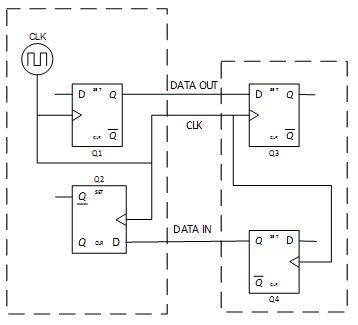

官方披露,JESD239GDDR7是第一款使用脉冲幅度调制(PAM)接口进行高频操作的JEDEC标准DRAM。其PAM3接口提高了高频操作的信噪比(SNR),同时提高了能效。通过使用3个电平(+1、0、-1)在2个周期内传输3个比特,而传统的NRZ(非归零)接口在2个周期内传输2个比特,PAM3在每个周期内提供了更高的数据传输速率,从而提高了性能。

相比GDDR6,GDDR7的带宽是其两倍,每个器件的带宽可达192 GB/s。这是通过增加独立通道数量至4个来实现的。GDDR7还支持16 Gbit至32 Gbit的密度,并包括支持双通道模式,可以将系统容量翻倍,可以满足未来图形、游戏、计算、网络和人工智能应用对高内存带宽不断增长的需求。

同时,核心独立的 LFSR(线性反馈移位寄存器)训练模式,带有眼罩和错误计数器,可提高训练精度,同时缩短训练时间。此外,通过整合最新的数据完整性功能,包括带实时报告的片上 ECC (ODECC)、数据中毒、错误检查和清理以及带命令阻塞的命令地址奇偶校验(CAPARBLK),满足 RAS(可靠性、可用性、可维护性)的市场需求。

在容量上,目前第一批GDDR7显存只有2GB(16Gb),和如今的GDDR6/6X一致,因此首发搭载的NVIDIA RTX 50系列、AMD RX 8000系列对于显卡的需求还较大。JEDEC表示,未来会有3GB、4GB、6GB甚至是8GB,其中3GB这种反常规容量是首次出现。

目前,AMD和NVIDIA都已经加入了这个新标准,而三星和美光也已经确定了下一代GDDR7内存模块的开发计划。三星的目标是实现32Gbps的速度,而美光则计划推出24Gb+32 Gbps的芯片。据悉,美光在其最新的路线图中也公布了到2026年达到36Gbps和24Gb+的内存模块。

LPDDR6内存规格今年第三季度敲定?

此外,近日韩媒etnews引援业内人士消息,新一代移动端 DRAM 内存规范 LPDDR6 有望今年 3 季度公布。

据悉,行业标准制定组织JEDEC固态技术协会近日在葡萄牙首都里斯本召开了下一代移动端随机存取处理器标准咨询会。此次会议中,与会各方进行了丰富的讨论,完成了 LPDDR6 标准的定稿工作,预计将于今年 3 季度正式发布。

公开资料显示,目前广泛使用的LPDDR5规范发布于2019年。而升级版 LPDDR5X 规范于 2021 年推出,进行了多项调整以实现更高速度,最高可达 8533Mbps。此外,SK海力士还推出了基于私有规范的 9.6Gbps LPDDR5T 产品,美光也推出了同等速率的 LPDDR5X 内存。

近年来,凭借其能效和速率优势,LPDDR 的市场从智能手机等传统产品逐步扩展至英伟达 Grace 处理器等部分服务器处理器,以及一些 AI 专用芯片。而随着 AI 的广泛应用,不仅移动产品需要相较 LPDDR5X 更高速的内存“喂饱”端侧 AI 模型,后两类处理器也需求更大的内存带宽。同时,三大用途对内存功耗均有着严苛的要求。行业人士表示,LPDDR6 标准的两大开发重点就是提高数据吞吐率和最小化功耗。

etnews消息称,高通骁龙8 Gen 4有望成为首款支持 LPDDR6 内存的产品。

二

HBM技术渐进,市场需求巨大

据TrendForce集邦咨询资深研究副总吴雅婷表示,目前2024年HBM(High Bandwidth Memory)市场主流为HBM3,NVIDIA新世代含B100或H200的规格则为最新HBM3e产品。不过,由于AI需求高涨,目前英伟达(NVIDIA)以及其他品牌的GPU或ASIC供应紧俏,除了CoWoS是供应瓶颈,HBM亦同,主要是HBM生产周期较DDR5更长,投片到产出与封装完成需要两个季度以上所致。

吴雅婷表示,目前NVIDIA现有主攻H100的存储器解决方案为HBM3,SK海力士是最主要供应商,然而供应不足以应付整体AI市场所需。至2023年末,三星以1Znm产品加入NVIDIA供应链,尽管比重仍小,但可视为三星于HBM3世代的首要斩获。

HBM3e预计下半年逐季放量,三星、美光加入供应行列

由于三星是AMD长期以来最重要的策略供应伙伴,2024年第一季,三星HBM3产品也陆续通过AMD MI300系列验证,其中包含其8h与12h产品,故自2024年第一季以后,三星HBM3产品将会逐渐放量。值得注意的是,过去在HBM3世代的产品竞争中,美光(Micron)始终没有加入供应行列,仅有两大韩系供应商独撑,且SK海力士HBM市占率目前为最高,三星将随着后续数个季度MI300逐季放量,市占率将急起直追。

而自2024年起,市场关注焦点即由HBM3转向HBM3e,预计下半年将逐季放量,并逐步成为HBM市场主流。据TrendForce集邦咨询调查,第一季由SK海力士率先通过验证,美光紧跟其后,并于第一季底开始递交HBM3e量产产品,以搭配计划在第二季末铺货的NVIDIA H200。三星由于递交样品的时程较其他两家供应商略晚,预计其HBM3e将于第一季末前通过验证,并于第二季开始正式出货。由于三星HBM3的验证已经有了突破,且HBM3e的验证若无意外也即将完成,这也意味着该公司的出货市占于今年末将与SK海力士拉近差距。

消息称JEDEC有望放宽HBM4标准,混合键合还在未来

据韩媒ZDNet Korea报道,行业标准制定组织 JEDEC 固态技术协会有望放宽对HBM4内存的高度限制,内存厂商无需被迫转向混合键合(Hybrid Bonding)。

据悉,JEDEC的主要参与者最近同意将HBM4产品的标准定为775微米(μm),比上一代的720微米更厚。据悉,该协议或将对三星电子、SK海力士、美光等主要内存制造商的未来封装投资趋势产生重大影响。

先进封装的意义旨在实现更大的互连密度(每个区域有更多的互连),减少迹线长度(trace length )以降低每比特传输的延迟和能量。作为先进封装技术中的显眼存在,自诞生起,混合键合就被寄予厚望。

混合键合用于芯片的垂直(或 3D)堆叠。混合键合的显著特点是它是无凸块的。它从基于焊料的凸块技术转向直接铜对铜连接。这意味着顶部die和底部die彼此齐平。两个芯片都没有凸块,而是只有可缩放至超细间距的铜焊盘。没有焊料,因此避免了与焊料相关的问题。与以前的基于凸块的互连相比,混合键合引入了一系列全新的技术和工艺挑战。为了实现高质量的键合,对表面光滑度、清洁度和粘合对准精度有非常严格的要求。

业界曾有言“混合键合将成为自EUV以来半导体制造最具变革性的创新”,事实是否如何我们目前还不可得知,但是,可以看到的是三星电子、SK海力士、美光都在你追我赶,争相发力进一步突破这种技术。

假如JEDEC放宽对HBM4内存的高度限制,内存厂商无需着急键合技术的飞跃。如果封装厚度为775微米,使用现有的键合技术如引线键合、倒装芯片键合和硅通孔(TSV)键合等就可以充分实现16层DRAM堆叠HBM4。毕竟解决当下市场竞争问题还是必要的。并且考虑到混合键合的投资成本巨大,存储器公司很可能将重点放在升级现有键合技术上。

但是值得注意的是,上述提到的键合技术有其局限性,并不能很好的适配未来3D封装日益增长的复杂性和性能要求。目前,半导体产业链上下游都对混合键合技术变革充满期待,随着先进制程研发愈演愈烈,混合键合技术的市场在未来值得期待。

评论