新思Fusion Compiler协助客户实现超过500次投片

新思科技宣布其旗舰产品Fusion Compiler RTL至GDSII解决方案自 2019推出以来,已协助用户累积超过500次投片,此项成就扩展了新思科技在数字设计实作领域的地位。使用 Fusion Compiler进行设计投片的客户涵盖领先业界的半导体公司40至3奈米制程节点,横跨高效能运算(high-performance computing; HPC)、人工智能(AI)与第五代行动通讯等高成长的垂直市场。

新思科技Fusion Compiler具备统一架构和优化引擎,可促进达成签核准确度(signoff-accurate)的性能、功耗和面积(PPA)指标,同时将设计迭代(design iteration)与后期意外降至最低。尤其是面对先进制程与极具挑战的项目进度,此解决方案可协助解决现今设计人员为满足严格的 PPA 目标所面临的重大挑战。与竞争对手的解决方案相较,客户可因此平均平均提高20%的效能、降低15%的功耗以及减少5%的面积。

三星电子系统LSI事业部设计技术团队副总裁Ilyong Kim表示:「新思科技Fusion Compiler无缝的生产部署提供绝佳的结果质量,包括芯片使用率的大幅提升以及加速上市时程,有助于提升我们的领导地位。其独特的单一数据模型和统一引擎,以及能消除设计迭代(design iteration)的内建签核时序(signoff timing)、寄生萃取(parasitic extraction)和功耗分析,让Fusion Compiler有别于业界其他解决方案。多次成功的设计投片让我们不断感受到Fusion Compiler所带来的效益,目前我们正扩大部署该解决方案,包括采用最新的机器学习技术,以进一步深化我们以客户为中心的市场区隔。」

日本铠侠株式会社设计技术创新部资深经理Kazunari Horikawa表示:「身处于竞争激烈的半导体领域,铠侠株式会社作为内存领导厂商,在高效能功耗比(performance-per-watt)的内存控制器领域处于领先地位。我们与新思科技的合作伙伴关系实现了完整的Fusion Compiler设计流程,并大幅提高了流程效率。此外,新思科技「融合设计平台」(Fusion Design Platform)技术辅以TestMAX让我们加速设计方法,并在最新投片中降低达40%的功耗以及缩小10%的面积,有助于提升我们的领导地位。我们期待与新思科技合作,进一步透过Fusion Compiler提高生产力。」

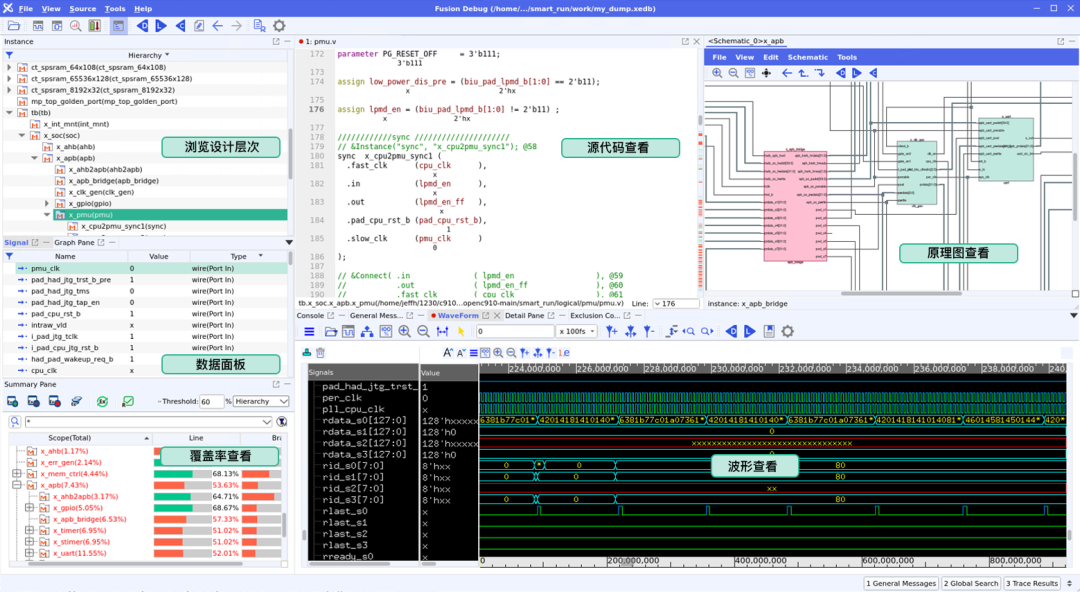

Fusion Compiler是业界唯一的单一数据模型并具备黄金签核(golden-signoff)的RTL至GDSII实作产品,其采用可高度扩展的统一数据模型,并包含了运用业界黄金签核(golden-signoff)分析工具技术的分析骨干。将上述功能全部集结在单一的整合接口(integrated shell)中,可针对可预测的结果质量(QoR) 与签核相关性(signoff correlation)提供独特的客制化流程。此外, 「无处不在的机器学习(machine learning everywhere)」技术强化其独特的架构,促使生产力和结果质量(QoR)达到更高的水平。

新思科技硅晶实现事业群营销策略副总裁Sanjay Bali表示:「我们的客户面临不断的压力,要在紧迫时程内将解决方案推向新市场。Fusion Compiler让他们加快产品推向市场的时间,同时带来最具差异化的PPA。看到客户使用Fusion Compiler实现超过500次投片,再次证明能为客户提供最佳PPA的垂直整合之RTL至GDSII解决方案有其市场需求。」

Fusion Compiler数字设计实作解决方案是新思科技「融合设计平台」(Fusion Design Platform)的核心,为业界第一个AI强化、云端就绪(cloud-ready)的设计解决方案,重新定义合成(synthesis)、布局绕线与签核等传统 EDA 工具的界线。该平台利用机器学习加速运算密集的分析并藉此预测结果以强化决策,同时利用先前的学习以达到更好的结果。

评论