- 新思科技宣布其旗舰产品Fusion Compiler RTL至GDSII解决方案自 2019推出以来,已协助用户累积超过500次投片,此项成就扩展了新思科技在数字设计实作领域的地位。使用 Fusion Compiler进行设计投片的客户涵盖领先业界的半导体公司40至3奈米制程节点,横跨高效能运算(high-performance computing; HPC)、人工智能(AI)与第五代行动通讯等高成长的垂直市场。新思科技Fusion Compiler具备统一架构和优化引擎,可促进达成签核准确度(signo

- 关键字:

新思 Fusion Compiler

- 要点: 作为新思科技Fusion Platform的一部分,IC Compiler II凭借其行业领先的容量和吞吐量,加速实现了包含超过590亿个晶体管的超大规模Colossus IPU新思科技RTL-to-GDS流程中针对AI硬件设计的创新优化技术提供了同类最佳的性能、功率和区域(PPA)指标集成式黄金签核技术带来可预测且收敛的融合设计,同时实现零裕度流程新思科技(Synopsys, Inc., 纳斯达克股票代码:SNPS)近日宣布,其行业领先的IC Compiler™ II布局布线解决方案成

- 关键字:

新思科技 IC Compiler II Graphcore

- 重点:3DIC Compiler基于新思科技的Fusion Design Platform、世界级引擎和数据模型,在单一用户环境下提供一个综合性的端到端解决方案,具有针对先进多裸晶芯片系统设计的全套功能提供强大的三维视图功能,为2.5D/3D封装可视化提供直观的环境,显著减少设计到分析的迭代次数,并最大限度地缩短整体集成时间提供与Ansys硅-封装-印刷电路板技术的紧密集成,以进行系统级信号、功率和热量分析新思科技(Synopsys, Inc.,纳斯达克股票代码:SNPS)近日推出其3DIC

Co

- 关键字:

新思科技 3DIC Compiler

- 重点:IC Compiler II和Fusion Compiler的机器学习技术助力三星将频率提高高达5%,功耗降低5%机器学习预测性技术可加快周转时间(TAT),使三星能够跟上具挑战性的设计时间表三星在即将推出的新一代移动芯片流片中部署了机器学习技术新思科技(Synopsys,

Inc.,纳斯达克股票代码:SNPS)今天宣布,三星(Samsung)为其新一代5纳米移动芯片生产设计,采用了IC Compiler™

II布局布线解决方案(新思科技Fusion Design

Platform™的一

- 关键字:

三星 新思科技 IC Compiler II 机器学习 5纳米 SoC

- 半导体设计、验证和制造的软件及知识产权(IP)供应商新思科技有限公司(Nasdaq:SNPS)日前宣布:该公司在其Galaxytrade;设计实现平台中推出了最新的创新RTL综合工具Design Compilerreg; 2010,它将综合和物理层实

- 关键字:

Compiler Design 布局

- 新思科技(Synopsys, Inc.)日前发布全新定制设计解决方案Custom Compiler™。Custom Compiler™将定制设计任务时间由数天缩短至数小时,消弭了FinFET的生产力差距。为了将FinFET版图生产力提升到新的高度,Synopsys采用了新颖的定制设计方法,即开发视觉辅助自动化技术,从而提高普通设计任务的速度,降低迭代次数并支持复用。通过与行业领先的客户的密切合作,Custom Compiler已经在最先进的节点上进行生产工作,并

- 关键字:

新思 Custom Compiler

- 半导体设计、验证和制造的软件及知识产权(IP)供应商新思科技有限公司(Nasdaq:SNPS)日前宣布:该公司在其Galaxytrade;设计实现平台中推出了最新的创新RTL综合工具Design Compilerreg; 2010,它将综合和物理层实

- 关键字:

Compiler Design 2010 布局

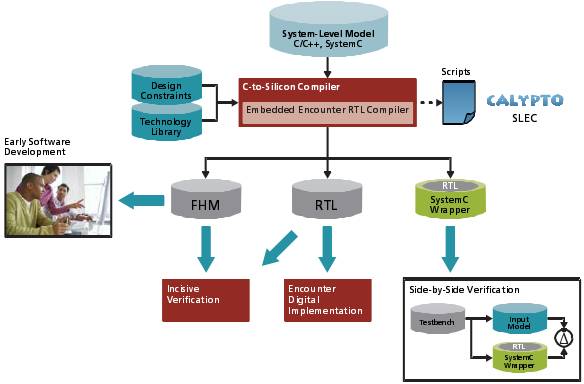

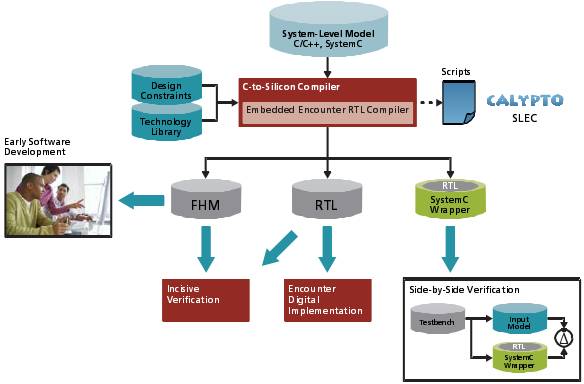

- 加州圣荷塞,2008年7月15日——全球电子设计创新领先企业Cadence设计系统公司(纳斯达克: CDNS),今天宣布推出Cadence® C-to-Silicon Compiler,这是一种高阶综合产品,能够让设计师在创建和复用系统级芯片IP的过程中,将生产力提高10倍。C-to-Silicon Compiler中的创新技术成为沟通系统级模型之间的桥梁,它们通常是用C/C++ 和SystemC写成的,而寄存器传输级(RTL)模型通常被用于检验、实现和集成SoC。这种

- 关键字:

Cadence SoC C-to-Silicon Compiler 半导体

- 全球电子设计创新领先企业Cadence设计系统公司(纳斯达克: CDNS),今天宣布推出Cadence® C-to-Silicon Compiler,这是一种高阶综合产品,能够让设计师在创建和复用系统级芯片IP的过程中,将生产力提高10倍。C-to-Silicon Compiler中的创新技术成为沟通系统级模型之间的桥梁,它们通常是用C/C++ 和SystemC写成的,而寄存器传输级(RTL)模型通常被用于检验、实现和集成SoC。这种重要的新功能对于开发新型SoC和系统级IP,用于消费电子、无

- 关键字:

Cadence C-to-Silicon Compiler

- Synopsys 今天发布了下一代布局布线解决方案——IC Complier 2007.03 版。该版本运行时间更快、容量更大、多角/多模优化(MCMM)更加智能、而且具有改进的可预测性,可显著提高设计人员的生产效率。

同时,新版本还推出了支持正在兴起的45纳米技术的物理设计。目前,有近百个采用IC Compiler的客户设计正在进行中,订单金额超过一亿美元。IC Compiler正成为越来越多市场领先的IC设计公司在各种应用和广泛硅技术中的理想选择。2007.03 版的重大技术创新将为加速其广

- 关键字:

COMPILER Synopsys 单片机 嵌入式系统

- 易于移植、强有力的技术发展路线图等优势使其在竞争中脱颖而出 全球电子设计自动化软件工具(EDA)领导厂商Synopsys(Nasdaq: SNPS)近日宣布,美国威捷半导体公司(Silicon Optix)采用Synopsys IC Compiler下一代布局布线解决方案,设计其高性能视频处理器。长期以来,威捷半导体一直是Synopsys布局布线技术的用户。为了转向90纳米工艺,威捷半导体评估了市场上所有的解决方案,并最终选定了IC Compiler,这是

- 关键字:

90纳米设计 Compiler IC Synopsys 单片机 嵌入式系统 威捷半导体

compiler介绍

您好,目前还没有人创建词条compiler!

欢迎您创建该词条,阐述对compiler的理解,并与今后在此搜索compiler的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473