基于FPGA的单线聚合(SWA)

在电子系统中,用于连接电路板和各个模块之间的连接器不仅价格昂贵而且占据了电路板和系统的宝贵空间,并且它们还会降低产品的稳定性。

本文引用地址:https://www.eepw.com.cn/article/202010/419456.htm莱迪思开发了一种创新的方法,让系统架构师和开发人员使用尺寸极小的低功耗FPGA来大幅度减少板间和模块间的连接器数量,在增加系统稳定性的同时,降低了空间占用和成本。

拥有FPGA设计经验的开发者还能自定义该解决方案。即便没有FPGA设计经验,开发人员依然能够轻松快速完成部署。

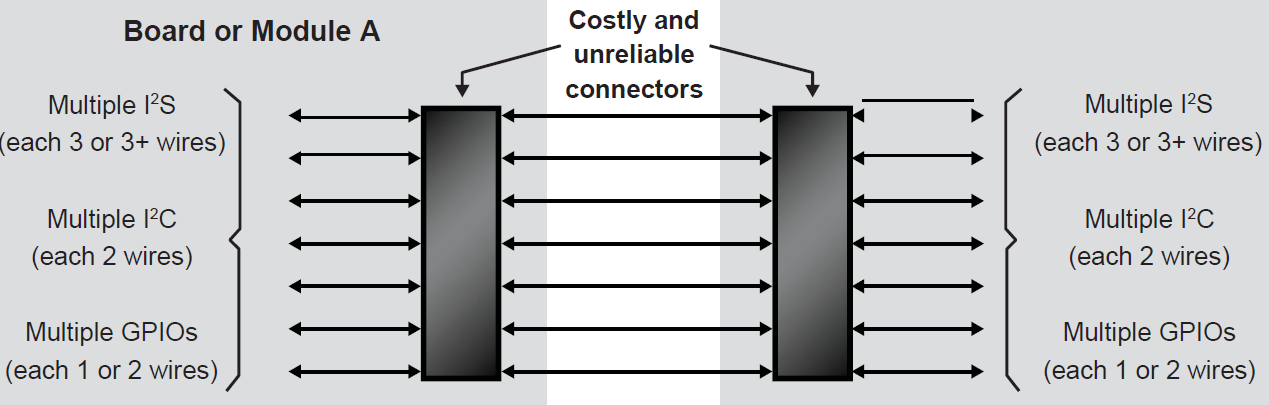

图1 传统的连接器不仅价格高、占用空间,而且会降低系统稳定性

优化连接

当今的绝大多数电子系统都包含两个及以上的电路板和/或模块。(除非另有说明,否则下文中的术语“电路板”或“板”将默认包括“模块”。)

对于系统设计师而言,经常面临的问题就是连接电路板进行数据传输。常见的解决方案是将多引脚连接器安装在电路板上,然后使用多个线束或导线将电路板连接在一起。

然而,每个连接器的引脚都是潜在的故障点,因此,除了增加成本和占用空间外,连接器通常还是影响 电子系统可靠性的关键因素。这意味着最大程度减少板间连接可以降低成本、减小空间占用并提高系统稳定性。

如图1所示,这些电路板之间信号的通信速率相对较低,使用的是通用I/O(GPIO)或者I2C和I2S等串行接口。

各种系统的设计人员——从手持设备、笔记本电脑到工业控制器——都迫切希望最大程度减少连接器引脚数量和电路板之间的连线。

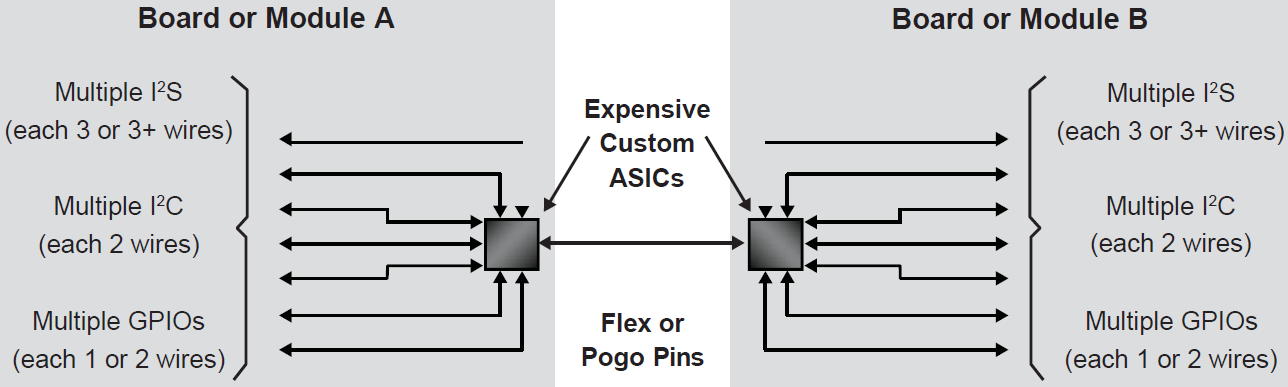

图2 开发定制ASIC价格昂贵且耗时,且非常不灵活

单线聚合:FPGA的优势

单线聚合(SWA)背后的原理是将多个信号汇聚到一个时分复用(TDM)信号中,而该信号在电路板间传输仅需要一根线缆。实现该方案的一个做法是为每种产品创建定制的专用集成电路(ASIC)(图2)。

然而,定制ASIC的解决方案有许多缺点,如开发成本高昂且耗时。更糟的是,它们所包含的任何算法和功能实际上都是“冻结在芯片中”,这意味着它们无法适应不断变化的需求。例如销售主管突然宣布:“我们最大的客户说需要用两个I2C通道替代其中一个I2S接口。”

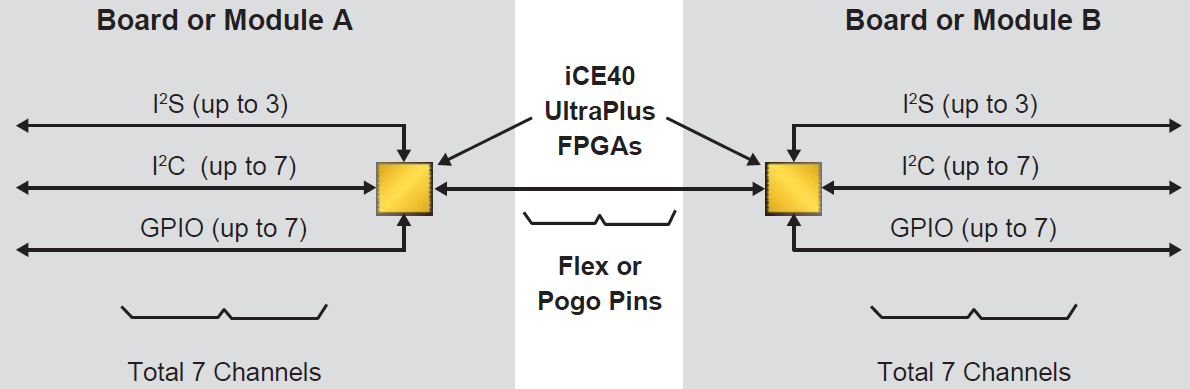

理想的解决方案是采用低成本的现场可编程门阵列(FPGA),如莱迪思半导体的iCE40 UltraPlus™器件(图3)。

使用FPGA实现单线聚合功能的一个巨大优势是它们非常灵活,可以快速轻松地进行定制设计,从而实现所需数量和类型的各种通道。

图3 FPGA价格较低且非常灵活

FPGA设计人员使用iCE40 UltraPlus实现单线聚合

上一段中有这样一句表述: “基于FPGA的单线聚合可以快速轻松地进行定制设计”。这句话有个前提那就是需要非常熟悉FPGA设计。

如果您是FPGA设计人员,莱迪思可为您提供行业最易于使用的FPGA开发工具。此外,在单线聚合解决方案中,莱迪思还提供全套参考设计资源,搭配其行业领先的iCE40 UltraPlus™ FPGA:

● 易于修改、参数化的单线聚合参考设计的源代码,可在莱迪思Radiant设计工具上运行

● 免费使用Lattice Radiant®设计工具

● 相关的参考设计用户指南

● 单线聚合演示和开发板

然而,并非所有的设计团队都有FPGA设计经验。幸好,莱迪思也专为非FPGA设计人员提供解决方案。

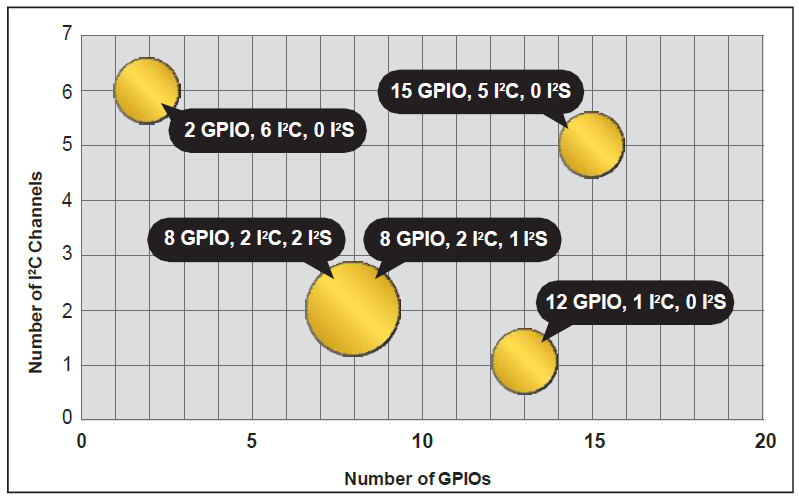

图4 提供预编译的位流,拥有五种常见配置

非FPGA设计人员使用iCE40 UltraPlus实现单线聚合

拿一个基于微控制器(MCU)的系统举例。设计团队的某些成员可以熟练使用C或C ++之类的语言来开发软件,然后运行软件编译器,软件编译器以机器代码生成可执行文件。团队的其他成员只需将此机器代码文件加载到MCU中,无须了解编程相关的任何信息。

同样,FPGA开发人员的专长是使用Verilog或VHDL等硬件描述语言(HDL) 描述设计,然后运行被称之为逻辑综合引擎的硬件编译器,将HDL生成配置文件,也就是常说的位流。团队的其他成员可以将位流载入FPGA,无需了解关于FPGA设计的任何内容。

首个针对非FPGA设计人员的单线聚合解决方案提供了五种预先综合的位流(图4)。这些配置是对诸多实际应用分析的结果,可以满足各类系统设计的要求。

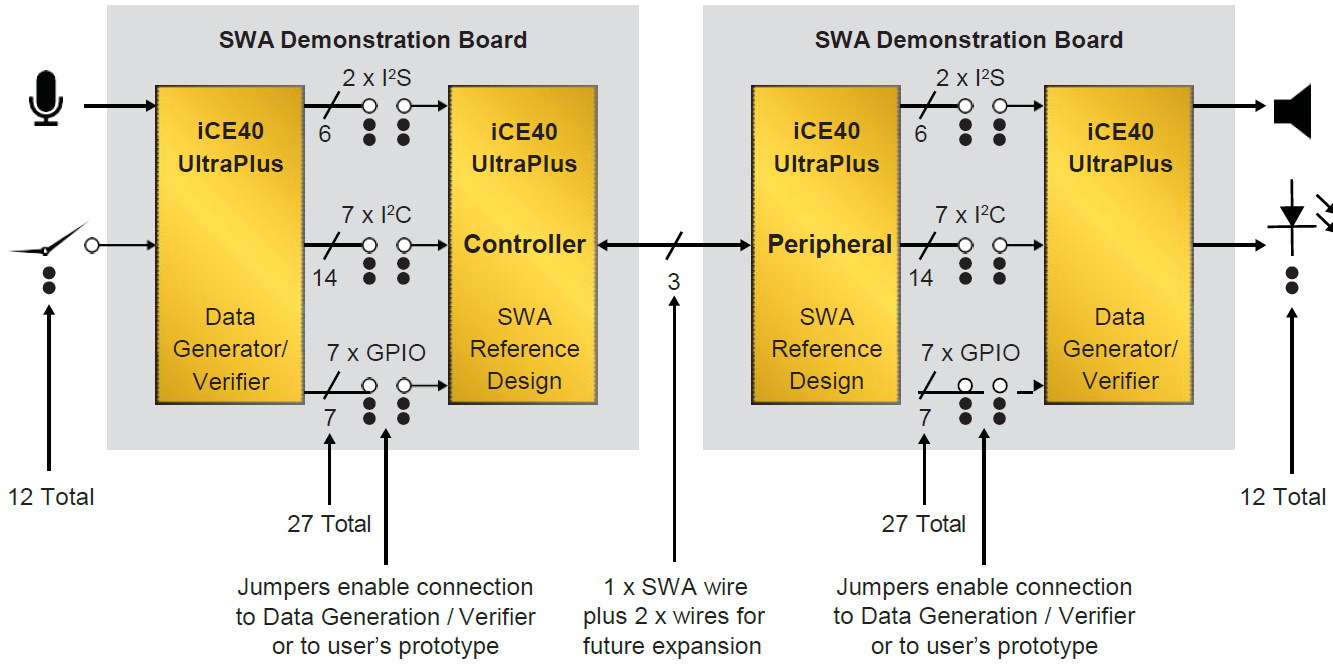

图5 单线聚合演示和开发板配置框图

iCE40 UltraPlus FPGA

为了更好地阐述本文内容,我们需要简单了解一下实现单线聚合的器件。iCE40 UltraPlus FPGA拥有灵活的逻辑架构、2800或5280个4输入查找表(LUT)、可定制的通用I/O(GPIO)、多达80 Kb的嵌入式存储块(EBM)和多达1 Mb嵌入式SRAM。

iCE40 UltraPlus FPGA可以在大多数应用中实现超低功耗的高级处理功能,其静态电流低至75 uA,工作电流低至1-10 mA。此外iCE40 UltraPlus FPGA还提供多种封装选项,满足各类应用的需求:2.15 x 2.50 mm超小尺寸WLCSP封装专为消费电子和物联网设备优化,0.5 mm引脚间距的7 x 7 mm QFN封装则可以满足成本优化型应用的需求。

由于配置位流可以直接加载到基于SRAM的配置单元中,因此iCE40 UltraPlus FPGA可以反复地重新编程。这样设计人员可尝试使用不同的设计和位流,是项目原型开发阶段的最佳选择。

如果在产品中使用基于SRAM的iCE40 UltraPlus器件,那么可以通过板上MCU或从外部SPI闪存设备来加载配置。

另外,iCE40 UltraPlus FPGA还包含一次性可编程(OTP)片上非易失性配置存储器(NVCM),非常适合大规模量产。对NVCM进行编程后,器件将自动、快速且安全地从该配置启动。

图6 两种应用案例

单线聚合演示和开发板

SWA演示和开发板包含两片iCE40 UltraPlus FPGA。一片用作数据生成器或数据验证器,另一片用于实现单线聚合参考设计(用作控制器或外设)。

图5展示了两块开发板的典型使用场景。在此案例中,左边的开发板包括了数据生成器和单线聚合控制器,右边的开发板则包括了单线聚合的外设和数据验证器。

单线聚合解决方案特性总结

如上所述,单线聚合参考设计在两片iCE40 UltraPlus FPGA上运行,其中一个FPGA以时分复用方式聚合多个数据流(例如I2C、I2S和GPIO),然后通过单线将其发送到另一个FPGA,解聚回原来的数据流。

两片FPGA之间的单线通信速度约为7.5 Mbps。该设计也可自行配置——可以调整I2C / I2S总线数量和GPIO数量以及单线协议数据包的长度,并且FPGA之间的单线协议拥有错误检测和重试功能。该解决方案的特性的简要概述如下:

● 最多聚合7个通道

● 单线上的原始数据速率约为7.5 Mbps或更高

● 数据包长度可变,可有效利用单线带宽

● 接收端出现奇偶校检错误时可重新进行传输

● 支持I2C的Fast-mode (400 kbps)和Fast-mode Plus(1 Mbps)

● I2C中断可以使用GPIO和基于事件的传输来实现

● I2S支持单个立体声通道、48K hz采样速率、高达32位采样以及双向支持

小结

当今的许多电子系统都包括多块电路板。此外,这些系统大多使用多种不同类型接口(例如I2C、I2S和GPIO)从外围设备和传感器收集数据,并在电路板之间传输。

在拥挤的电路板和连接器上传输信号本身可能会带来很多问题,除此之外,电路板的面积和系统内部空间通常十分宝贵。除了增加成本和占用空间外,连接器通常还是系统中最不可靠的组件。

莱迪思开发了一种创新的方法让系统架构师和开发人员使用小尺寸、低成本的FPGA来实现单线聚合,显著减少板间连接器的数量,在提高系统稳定性的同时还减小了系统尺寸和成本。

拥有FPGA设计经验的开发人员可以自定义该解决方案。此外,即便没有任何FPGA开发经验,开发人员也能快速轻松地完成部署。

评论