不对称内核的引导固件体系结构

摘要

本文引用地址:https://www.eepw.com.cn/article/201808/387566.htm过去,支持不同计算内核(对称/不对称架构)的处理器通常从一个特定的内核(一般为主内核或内核0)引导。由于经济增长放缓,半导体公司力求创新,寻求不同的方式和方法提高经济效益,增加其毛利率。片上系统(SoC)解决方案旨在满足多个领域的要求。如支持不对称引导,各个公司可使用相同的光刻掩模将SoC的目标范围扩展到各个不同的市场。

概述

人们对互连世界的渴望催生了独特的系统架构设计,包括使用同构或异构计算架构的单核系统及多核架构。

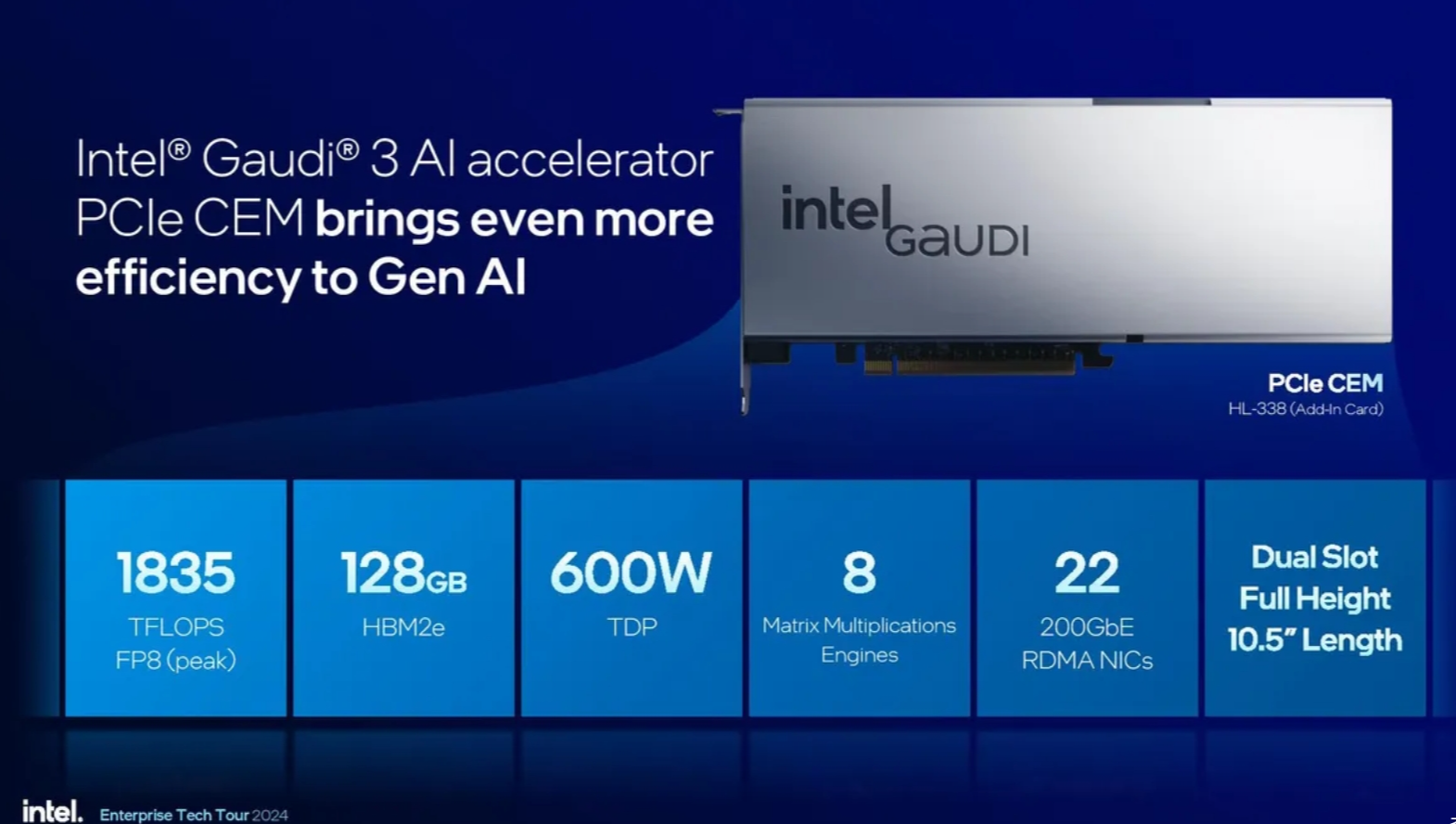

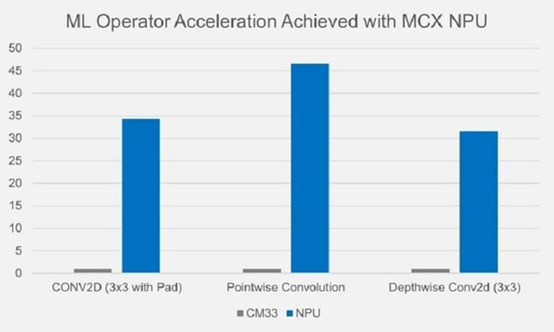

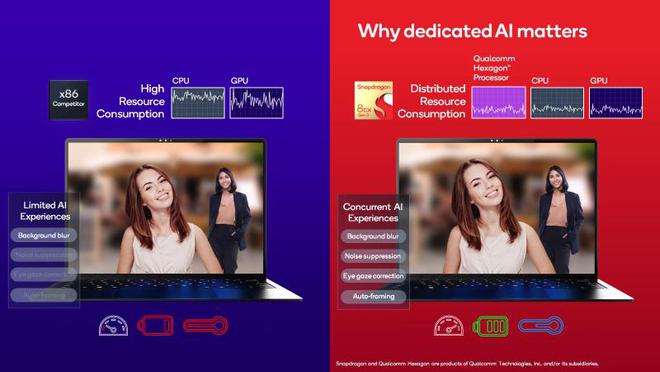

目前设计的复杂应用需要支持在系统中执行特定功能的特殊硬件加速器。这些以ASIC(特定用途集成电路)、FPGA(现场可编程门阵列)、GPU(图形处理单元)等形式实现。这些不同的功能单元大多采用不同的指令集架构(ISA)。

背景

过去,支持不同计算内核(对称/不对称架构)的处理器通常从一个特定的内核(一般指定为主内核或内核0)引导。由于经济增长放缓,半导体公司力求创新,寻求不同的方式和方法来提高经济效益,增加其毛利率。片上系统(SoC)解决方案旨在满足多个领域的要求。如支持不对称引导,各个公司可使用相同的光刻掩模将SoC的目标范围扩展到各个不同的市场。例如,如果一个SoC有一个应用处理器(AP)和一个实时控制器内核,SoC可从AP或实时控制器引导,同一个SoC不仅可用于高性能(采用AP引导方式)应用,还可用于关键任务(低延迟、关键时间应用)应用。

什么是不对称内核?

不对称内核是指一个系统的两个及以上的处理元件或单元拥有不同的指令集架构(ISA)。这些内核为整个系统提供特定的功能,如改善系统的处理能力或加快系统的反应速度等。

因此不对称内核系统软件设计就成了一个难题。如果SoC支持从多个内核引导,问题则变得更加复杂。第一个问题是引导体系结构。本文阐述采用不对称内核架构的引导固件设计。

引导体系结构的设计标准

在定义此类系统的引导体系结构时会遇到各种问题,不是每个问题都有通用的解决方案。有时一个解决方案还需要硬件支持。以下是设计人员遇到的一些设计问题:

● 指令集架构(ISA)兼容性

● 上电复位向量位置

指令集架构兼容性

第一个也是最重要的设计挑战是不同内核的指令集架构(ISA)兼容性问题。ISA是指硬件和软件之间的边界。ISA用于将助记符转换成机器语言(能够被处理器理解)。

根据ISA,引导体系结构可分为两个部分:

a.ISA不兼容

这意味着为一个内核编写的软件无法被其它内核理解。在此类系统中,引导代码对不同的内核是完全不同的。

b.ISA部分兼容

这意味着不同的内核支持一个共同的ISA版本,例如,包含ARM Cortex-A和Cortex-M内核的系统。对于此类系统,引导代码分为两部分。

● 第一部分是特定内核的引导代码,实现单个内核的特定软件功能。

● 第二部分是采用通用ISA实现的公共引导代码,实现批量引导功能。该软件调用第一部分实现的特定内核的软件。

许多处理器架构采用处理器ID或CPU ID等寄存器。SoC设计人员针对不同的内核对该寄存器赋予不同的值。通过读取该处理器ID寄存器来识别内核类型。根据该寄存器,引导代码可决定实现特定内核的功能。要点是公共引导代码可在不同内核上执行相同的指令,再根据执行内核产生不同的结果。

● 公共寄存器:

如果该寄存器是内存映射的,那么访问该寄存器的地址对于所有内核都必须相同。例如,在对接ARM Cortex-Ax和Cortex-Mx时,处理器ID寄存器通过不同的助记符访问。因此,在此类SOC设计中需要采用内存映射寄存器,识别执行内核的机制也与硬件相关。

● 使用相同的指令读取处理器ID/CPU ID:

在某些情况下,将寄存器作为某种特殊目的寄存器(Special Purpose Register)(如在PowerPC的情况下)。应注意,相同的指令可用于通过不同的内核访问该寄存器。例如,当在SoC中集成Z2和Z4 PowerPC内核时,用SPR 286寄存器访问处理器ID。

上电复位向量位置

上电复位向量位置表示加载到内核程序计数器的地址,当内核复位后从该地址提取第一个指令,这对不对称内核SoC引导体系结构提出了一个重大的设计挑战。包含多个内核的SoC可设计为从任何可用内核进行引导。大多数情况下,从哪个内核引导是可配置的,但是,由于引导软件驻留到微处理器的ROM区域,因此引导软件应能够在选定的引导内核上运行。

那么复位向量位置为引导软件带来了什么挑战呢?对称内核是绝对没有问题的。这是因为对于对称内核来说,引导向量位置解析是相同的。但是,对于不对称内核来说,则会产生问题,这有两个主要原因:

● 复位向量对于所有可引导的内核都不同。

● 两个或以上可引导的不对称内核有一个公共的复位向量位置。

复位向量对于所有可引导的内核都不同

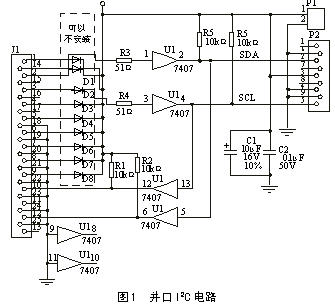

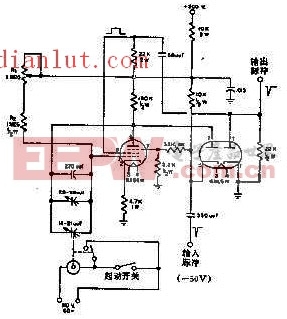

如果复位向量对于所有可引导的内核都不同,那么这个问题的解决方案可在引导软件中实现,如下图所示。引导软件将位于ROM内存区的不同位置,内核在上电复位后将从该位置跳转。

两个或以上可引导的不对称内核有一个公共的复位向量位置

当各种不对称可引导内核共享复位向量时,问题会变复杂。

● 复位向量位置解析

即使复位向量位置对于两个或以上不对称内核是相同的,然而,复位向量位置可用的数据的解析对于不同的内核可能会不同。例如,如果一个SoC有两个不对称内核Cortex-Ax和Cortex-Mx,那么复位向量位置对于这两个内核均为0x0000_0000。该地址可用的数据被这两个内核以不同的方式解析。Cortex-Ax将该数据解析为一个指令,导致跳转到引导固件代码将驻留的位置。但同样的数据被Cortex-Mx内核解析为堆栈指针。

● 指令集架构不兼容

复位向量位置呈现的代码可被一个内核理解,但无法被另一个内核理解。这可能会产生异常,或者使不能理解代码的内核进入不可预知的状态。

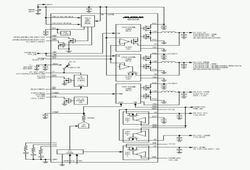

在这种情况下,人们可能想把失败内核的复位向量位置转到不同的地址位置,即映射到闪存或任何非易失性存储器位置。不能仅在软件设计中解决此类问题,还需要硬件支持。该解决方案需要SoC硬件的地址转换逻辑,将所有可引导不对称内核总线上的复位向量地址转换为复位向量表驻留的ROM存储器区的不同位置。

结束语

本文展示了为不对称内核系统设计引导体系结构的不同设计方法。此类系统的设计方法不限于本文所述内容,但主要受SOC设计的限制。设计人员甚至可以根据硬件架构结合使用所述不同方法。

评论