ARM Cortex-A 移动处理器发展概览

简介

本文引用地址:https://www.eepw.com.cn/article/201710/367207.htmARM Cortex-A 移动应用处理器产品线横跨了几代产品和三个主要产品类别。有些开发人员和 SoC 设计人员经历了一款或多款新型 ARM 处理器的推出过程,他们知道该产品线如何从单个高性能通用 CPU 设计演进成为三个不同产品线,分别面向高端、中端、入门级的移动设备 SoC 市场,这让他们受益匪浅。

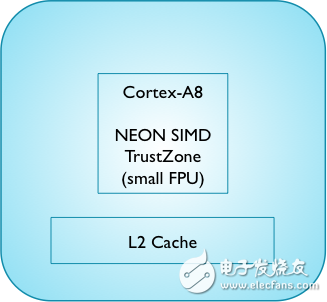

Cortex-A8

ARM 在 2005 年向市场推出 Cortex-A8 处理器,是第一款支持 armv7-a 架构的处理器。ARMv7 包括 3 个关键要素:NEON 单指令多数据 (SIMD) 单元、ARM trustZone 安全扩展、以及thumb2 指令集,通过 16 位和 32 位混合长度指令以减小代码长度。Cortex-A8 是 ARM 实现的第一个基于新ISA的超标量处理器:它实现了完全双发射流水线,这意味着 cortex-a8 能够同时发出在指令流中先后出现的任何两个没有数据依赖的指令。但是,它不能乱序来发射或撤销指令 –该功能在之后的设计中才被实现。

当我们推出 Cortex-A8 时,很多合作伙伴认为这款处理器放在移动电话上是大材小用,他们很自然地质疑道,“客户会在手机上浏览互联网?不太可能吧。”但是,我们和业界一些主要思想领袖合作,向客户将会需要的产品迈进,尤其是因为当 Cortex-A8 在 2008 年投入批量生产时,高带宽无线连接 (3G ) 已经问世,大屏幕也用于移动设备。创新的移动行业充分利用了该产品:Cortex-A8 芯片的推出正好赶上了智能手机出货量猛增的大好时机。

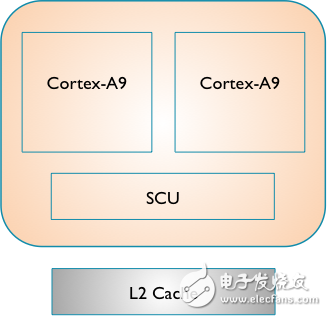

Cortex-A9

推出 Cortex-A8 之后不久,ARM 又推出了首款多核 ARMv7 CPU:cortex-a9。Cortex-A9 利用硬件模块来管理 CPU 集群中一至四个核心之间的高速缓存一致性,加入了一个外部二级高速缓存。理论上,客户可以设计不包括二级缓存的小型版本 Cortex-A9,这种设计允许剔除管理高速缓存一致性的逻辑模块,以实现尺寸更小的单核设计。但实际上,大多数设计都采用双核个或更多核心并附带二级高速缓存。此外,在2011 年底和 2012 年初,当移动 SoC 设计人员可以采用多个核心之后,提高性能的突破点从提高单核性能转移到提高核的数量。旗舰级高端移动 CPU迅速从最初的双核拓扑结构移至四核 Cortex-A9。

除了开启了多核性能大门之外,与 Cortex-A8 相比,每个 Cortex-A9 处理器的单时钟周期指令吞吐量提高了大约 25%。这个性能的提升是在保持相似功耗和芯片面积的前提下, 通过缩短流水线并乱序执行以及在流水线早期阶段集成neon SIMD 和浮点功能而实现的。

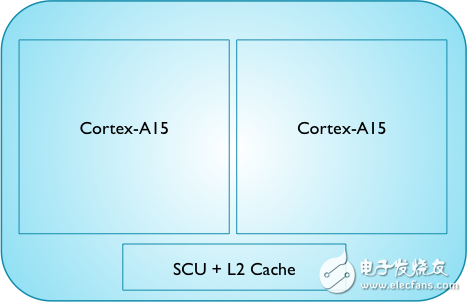

Cortex-A15

随着智能手机市场开始加速发展,ARM 再次预见到了不断发展的移动系统对芯片性能提出的更高要求。为此ARM开发了一款性能上大幅提升的处理器,用以专门针对新的高端移动市场。在已经非常强大的 Cortex-A9 的基础上,ARM 凭借 cortex-a15 又将性能提高了 50% 以上。此外,Cortex-A15 引入了一系列架构扩展,从而实现了更大物理地址空间、硬件虚拟化支持和扩展一致性。在 32 位系统中内存被划分为 2GB 设备内存和 2GB 普通内存,当设备的 RAM 超出2GB的时候,拥有更大的物理地址空间就变得异常重要。ARM和其他合作伙伴也一直在探索虚拟化技术在商务移动系统和自带设备中的用户操作系统以及类似应用情景进行探索。。扩展一致性在 big.LITTLE 处理器技术中被应用的淋漓尽致,它提供了一种降低平均功耗并在功耗受限的条件下优化达到最大性能的方法。

Cortex-A15 集群集成了监听控制单元 (SCU) 以实现硬件一致性,每个集群包含一至四个 CPU 核心,并集成二级高速缓存控制器 – Cortex-A15 之后的所有 ARM Cortex-A 系列 CPU 都沿用了这种拓扑结构。

在移动设备中不断突破性能极限

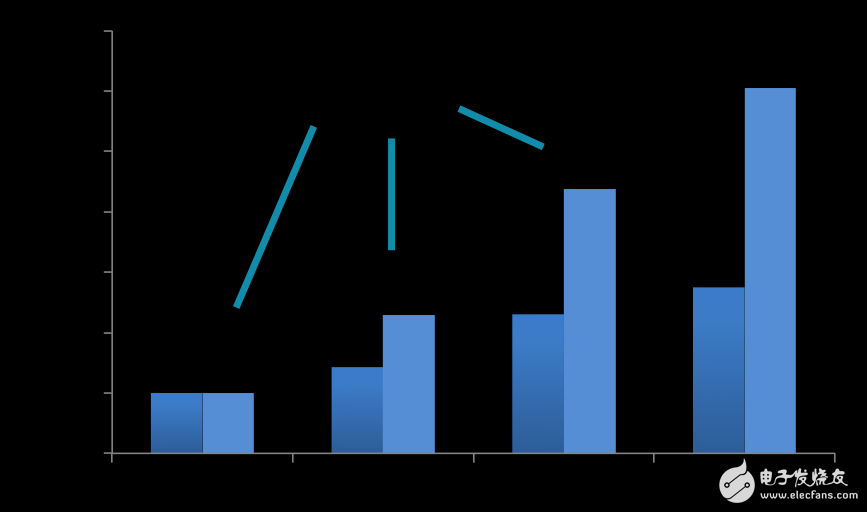

比较 Cortex-A 系列高端处理器的性能,可以看到自从 Cortex-A8 1GH 处理器在 2008 年上市以来,性能有了大幅提升。

一致性扩展机制,实现为 AMBA ACE, 使下图所示的big.little SoC成为可能。在 big.LITTLE 系统中,通常实现一个“大”CPU 集群,并对其进行调节以满足高性能的要求,同时对“小”的 CPU 集群进行调节,满足对高能效。在典型工作负载中,LITTLE 处理器可以处理绝大部分工作,而“big”CPU 集群的激活时间不足 10%,在很多情况下还达不到总 CPU 运行时间的 1%。通过 CoreLink CCI-400 高速缓存一致性互连组件,CPU 集群能够监听其他集群的高速缓存,从而实现软件线程从一个集群到另一集群的快速转移。

Cortex-A12

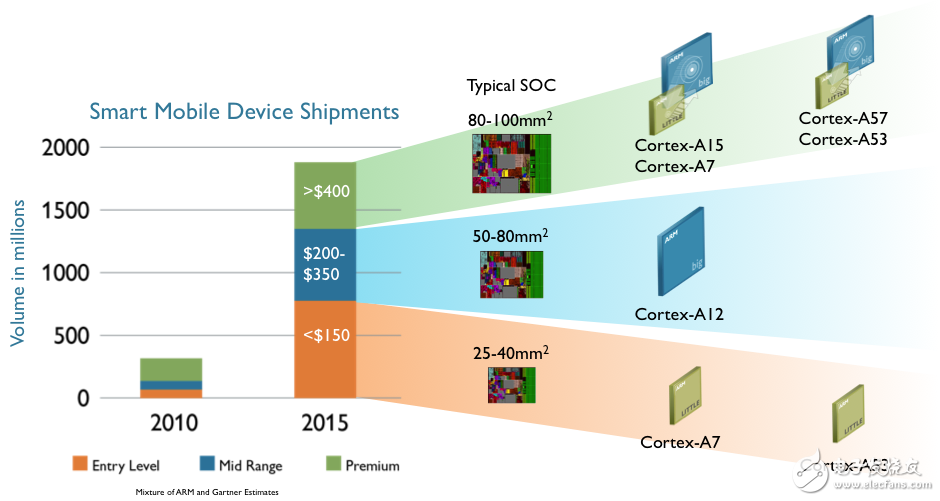

随着智能手机市场的爆炸式增长,SoC 供应商和 OEM 将该市场划分为旗舰高端级别、中端级别、低成本入门级别。随着这些细分市场的出现,ARM 一直在定义专门针对上述三个级别市场的不同处理器。cortex-a12 是采用全新微架构的一个全新处理器,专门面向快速发展的中端移动市场。下图显示了这些细分市场的规模,以及面向这些细分市场的 ARM Cortex-A 产品:

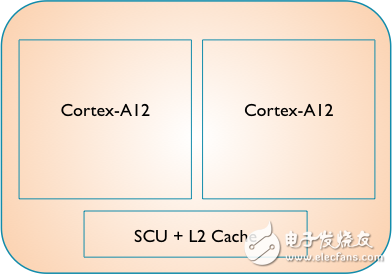

Cortex-A12 的设计面向中端移动 SoC,以满足这一细分市场对于芯片面积和功耗的要求。它使用无序双执行流水线,其性能比当前在许多中端移动 SoC 中使用的 Cortex-A9 高出 40%。Cortex-A12 在 2013 年中推向市场,有望在 2014 投入量产。它是一款 32 位处理器,具有与 Cortex-A15 相同的物理地址扩展和相关的架构特性。

Cortex-A12 能够在很多(但并非全部)用例中提供接近 Cortex-A15 的性能。Cortex-A12 还针对中端移动设计进行了优化,取消了一些企业功能,使用略微简单的流水线,因此在横跨多个市场的高端设备上都可以找到Cortex-A15的身影,而 Cortex-A12 则专门面向中端移动设计。

Cortex-A57

cortex-a57 是 ARM 针对 2013 年、2014 年和 2015 年设计起点的 CPU 产品系列的旗舰级 CPU,它采用 armv8-a 架构,提供 64 位功能,而且通过 Aarch32 执行状态,保持与 ARMv7 架构的完全后向兼容性。在高于 4GB 的内存广泛使用之前,64 位并不是移动系统真正必需的,即便到那时也可以使用扩展物理寻址技术来解决,但尽早推出 64 位,可以实现更长、更顺畅的软件迁移,让高性能应用程序能够充分利用更大虚拟地址范围来运行内容创建应用程序,例如视频编辑、照片编辑和增强现实。新架构可以运行 64 位操作系统,并在操作系统上无缝混合运行 32 位和 64 位应用程序。ARMv8 架构可以实现状态之间的轻松转换。

除了 ARMv8 的架构优势之外,Cortex-A57 还提高了单个时钟周期性能,比高性能 的Cortex-A15 CPU 高出了 20% 至 40%。它还改进了二级高速缓存的的设计以及内存系统的其他组件,极大的提高了能效。Cortex-A57 将为移动系统提供前所未有的高能效性能水平,而借助 big.LITTLE,SoC 能以很低的平均功耗做到这一点。

高效率产品线:Cortex-A5、Cortex-A7、Cortex-A53

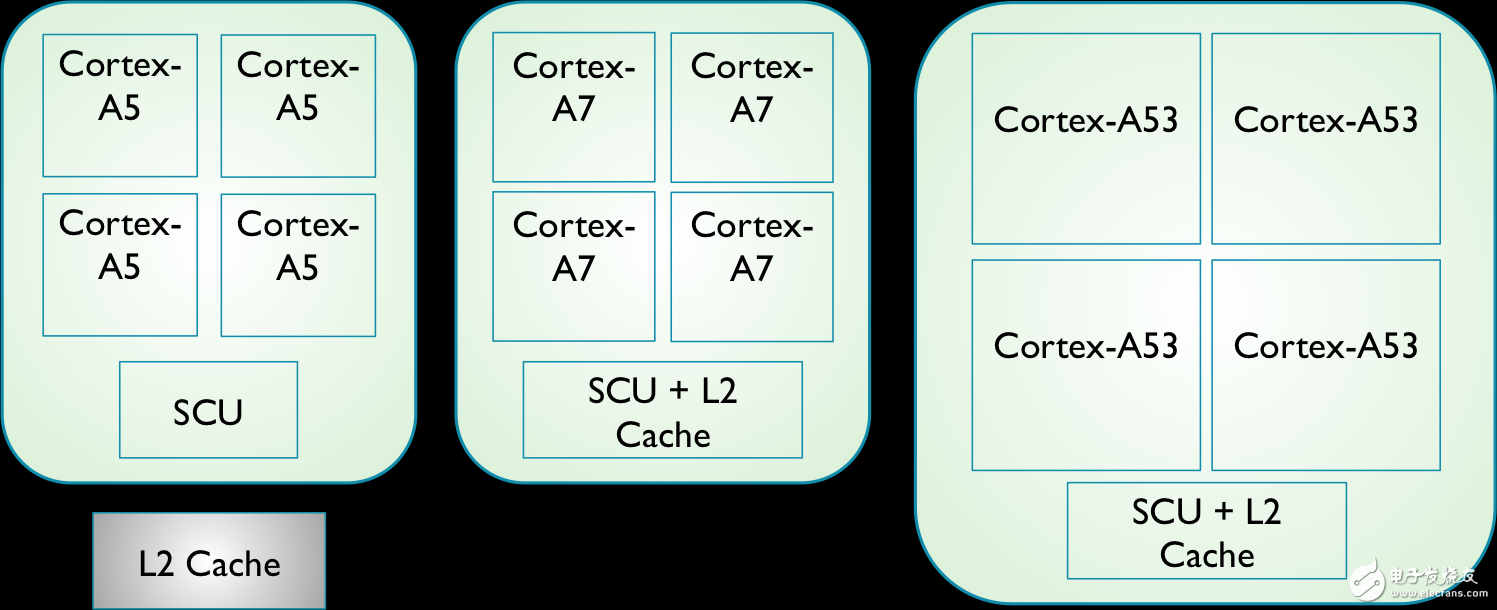

随着智能手机市场的崛起,最先出现的市场是入门级市场。在新兴市场,移动设备没有获得无线运营商的补贴,因此用户必须支付全价来购买移动设备,并且按月支付合约的服务费用。新兴市场的价格范围在 150 美元以下,并将很快降至 75 美元以下 – 我们需要一种不同类型的 SoC 设计来满足这些市场的需求。在 Cortex-A9 发布之后不久,ARM 试图开发一款处理器来满足这一市场需求:这款产品的尺寸和功耗与旧款 ARM926 等功能性手机处理器大致相同,但性能高于在第一代智能手机中使用的 arm11 系列。2009 年,我们发布了 Cortex-A5,该设计通过有序单执行 8 级流水线实现了上述目标。利用这种简单流水线设计,我们可将功耗保持在非常低的水平。而简化的功能集,造就了ARM 有史以来最高效的(每 mW 性能)应用处理器。

在 cortex-a5 取得成功的基础上ARM又设计了目前已在入门级智能手机中得到大量应用cortex-a7 处理器,形成了一个充满活力的智能手机处理器细分市场。随着 Cortex-A5 取得成功,下一个目标是开发能够匹配 Cortex-A15 的架构功能集的类似处理器,从而在 big.LITTLE 配对中将其与 Cortex-A15 结合使用。同时,该款处理器还应该在 Cortex-A5 的基础上提升性能,并具有与之相同的功效、和相似的功耗以及芯片大小。Cortex-A7 通过添加部分双执行,增加TLB 和内存结构,同时集成二级高速缓存,将单时钟周期性能提高了 20%。

高能效 CPU 产品线的最新成员利用了相同的 8 级有序流水线,但通过多种方式显著提升了性能,包括完全双执行流水线、更宽的内部总线、增强浮点和 SIMD 吞吐容量、更大的TLB,以及其他对存储器系统的改进。cortex-a53 包括可选 内部RAM ECC 保护,还提供外部总线选项,使得该处理器在移动和企业应用中都可以部署。

除了微架构性能改进之外,Cortex-A53 还增加了对 ARMv8 架构的支持,为独立入门级移动芯片设计,和包含多个 Cortex-A53 集群的可扩展企业应用引入 64 位功能,同时在高端移动系统中,将Cortex-A53和性能更强的Cortex-A57在big.LITTLE系统设计中配对使用。

下图显示了连续几代高能效Cortex-A CPU 的性能对比。因为采用最新的设计 Cortex-A53 能够提供比仅仅几年前的旗舰级 CPU (Cortex-A9)出色的多性能。下图显示的性能比较测试是在相同频率下进行的。在物理实现中,Cortex-A53、Cortex-A7 和 Cortex-A5 的 8 级流水线达到的频率和采用更长流水线的“big” Cortex-A CPU能达到的频率差距在15%之内。实际量产 SoC 频率存在很大差异,取决于流程选项和后端设计,我们已经看到 Cortex-A7 在采用 28nm制程下可以达到 1.2GHz、1.5GHz 甚至更高的频率。

有关 ARM 的高效率产品线的更多信息,请参阅 Kinjal Dave 的博客 – 高效率、中端或高性能 Cortex-A – 差异何在?

有关 Cortex-A53 的更多信息,请参阅我早期的关于最新高效率 Cortex-A CPU 的博客 – 有关 Cortex-A53 的 5 大必备知识

移动应用处理器全面路线图

本路线图将上述所有处理器都集中在单个图表中,展示了 ARM所提供的高性能级别、中端级别、入门级别的移动应用程序处理器,以及所支持的高速缓存一致性互联组件。

以上路线图展示了ARM 三个级别的移动应用处理器产品路线图,我们未来产品的开发也将继续遵循这一路线。我们专门针对高端、中端和高效率这三个细分市场的处理器设计,使我们能够提供针对这三级智能手机和平板电脑市场的定制产品。

为适当任务寻找适当处理器不再是难以决断的选择

ARM 的 big.LITTLE 技术旨在为消费者提供最佳整体用户体验 – 包括按需动态性能、更高的能效、“不发热”的耐用器件。市场上最早利用该技术的产品包括三星 GS4(国际版)和三星 Note 3(国际版)

下图显示了将在 2013 年和 2014 年推出的采用未来设计的高端移动 CPU 子系统,将在 2014 年和 2015 年的设备中使用。它采用 big.LITTLE 电源管理技术,利用 Cortex-A57 的强大性能,并且提供高速缓存一致性互联 (cci) 功能,能够为GPU 计算提供的 IO 一致性的支持。

有关 big.LITTLE 的更多详细信息,请参见我近期在 ARM TechCon 2013上进行的有关 big.LITTLE 平台测量结果的演示(旨在展示性能改进和节能):big.LITTLE 技术向完全异构全局任务调度迈进 - Techcon 演示文稿

另外,您可能希望阅读我早期论述该技术要点的博客 – 有关 big.LITTLE 的十大必备知识

以上系统示意图展示了最先进的移动 CPU 设计,它采用 Cortex-A57 和 Cortex-A53 处理器,并且结合最新的 mali_t760 GPU。请注意,它具有 2 个 big 核心。从我们已经进行的性能测试来看,2 个 big 核心似乎已经能满足当前工作负载。采用由Cortex-A15和Cortex-A7构成的当前最高端的移动 SoC的拓扑结构示意图和下图也是非常类似。Cortex-A50 系列处理器代表了将在 2014 年间问世的移动 SoC 的未来拓扑结构发展趋势 … 但 ARM 不会就此止步。我们将继续在低功耗 CPU、GPU 和系统设计领域开发新的创新技术,以此推动智能手机、平板电脑和新兴设备类型的创新,实现高效移动计算,提升全球数十亿用户的生活质量。

评论