协同创新 推动中国集成电路封测业发展

2017年7月25日,中国半导体行业协会集成电路分会秘书长、国家集成电路封测产业链技术创新战略联盟秘书长于燮康在《第十一届中国半导体行业协会半导体分立器件年会暨2017中国半导体器件创新产品与应用及产业发展论坛》做了《协同创新,推动中国集成电路封测业发展》的主旨报告。

本文引用地址:https://www.eepw.com.cn/article/201707/362232.htm

于燮康秘书长的报告共分三部分内容,第一部分回顾了中国集成电路封测业发展历程;第二部分讲述中国集成电路封测业的机遇和挑战;第三部分提出了未来中国集成电路封测业的发展途径--协同创新。

下面是根据于燮康秘书长演讲内容整理而成。

一、中国集成电路封测业发展历程

中国集成电路封测业在产业链中占据重要地位,在设计、芯片制造和封测三大产业中,封测业规模占比近年来一直高于国际上的普遍水平,2016年的占比达到36.1%。

中国集成电路封测业起步较晚,大体经历了以下4个阶段的发展过程:

第一阶段是初创阶段,大致时间是二十世纪80年代,这时期以通孔插装式封装为主,主要代表技术是DIP(双列直插封装)。于秘书长介绍说,中国的集成电路封装是华晶电子始于1978年。

第二阶段是重点发展阶段,大致时间是二十世纪90年代,进入了表面贴装时代,主要代表技术是SOP(小外形封装)、QFP(四方扁平封装),主要特点是引脚从两边或四边引出,安装方式改插装为表面贴装,较插装方式可大大提高引脚数和组装密度;这时期产业规模总体较小。

第三阶段是全面快速发展阶段,大致时间是二十一世纪初,在2006年之前,国内封测业已开始研究以焊球代替引脚和面阵列形式分布的表面贴装技术,主要代表技术是球栅阵列封装BGA和多芯片封装MCP等,在2006年至2010年期间,QFN、BGA、CSP等多项技术实现量产,与之前相比,封装技术有较大突破,产业规模已显著扩大,长电科技于2009年初次跻身全球十大封测业之列。

第四阶段是2011年至今的跨越式发展阶段,这一时期的技术特征是高密度和小型化,主要代表技术有晶圆级芯片尺寸封装(WLCSP)、倒装球焊阵列封装(FCBGA),特别是随着芯片特征尺寸已接近物理极限,原依靠减小特征尺寸来提高封装密度的方法遇到瓶颈的情况下,以3D封装、2.5D硅通孔为代表的封装技术应运而生,成为近年来封测业的一个技术亮点,总体技术水平与国际水平进一步缩小差距,部分封装技术已处于国际领先水平。

根据法国YOLE的研究数据表明,长电科技在先进封装制程方面以7.8%的份额排名全球第三,仅次于英特尔和矽品精密。

据封测联盟提供的2010年-2016年中国集成电路封测业的销售规模数据可以看出,中国集成电路封测产业得到快速发展,自2011年起的6年,销售收入比2010年增长了1.5倍,CAGR为16.39%。

于燮康秘书长表示,对国内外先进封装工艺技术水平比较而言,目前国内集成电路三大先进封装技术:SIP系统级封装(长电、华天)、WLP晶园级封装(长电、晶方)、FC倒装(长电、通富)封装技术均己具备并取得突破, 技术能力与国际先进水平基本接近,先进封装占比约20%, 但国内封装业总体仍以传统的中低端封装为主,其封装形式如SOP(SSOP、TSOP)、QFP(LQFP、TQFP)、QFN/DFN等。预计未来对高端先进封装技术的需求将愈来愈多。

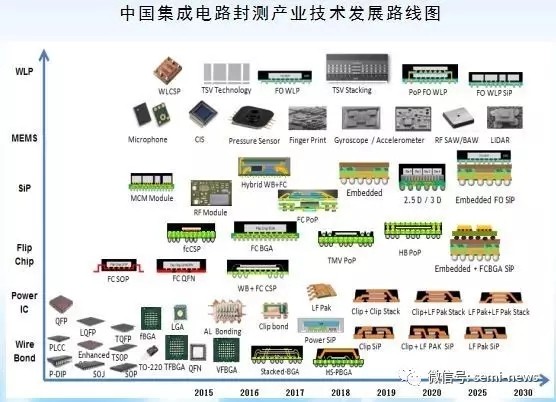

从封测联盟公布的《中国集成电路封测产业技术发展路线图》可以看出,我国在封装类型方面已经非常齐全。

从产业规模来看,多年来国内封测产业发展速度高于国际封测业整体发展的速度,但总体的封装技术水平与国际水平还存在不小的差距。

晶圆级封装(WLP)技术方面,国内主要采用 Fan-in技术,主要量产WLCSP产品;刚开始Fan-out的小规模量产,海外技术发展多样化,Fan-in、Fan-out、embedded WLP以及晶圆级3D堆叠封装技术已经成熟。

倒装(FC)技术方面,国内企业全部是采用传统的mass reflow技术。海外企业已经量产TCB键合的FC封装技术。国内本土企业组装芯片尺寸,还没有超过20x20mm的芯片。国外企业在贴装精度和稳定性方面有优势,例如环球仪器对于倒装芯片装配的设备解决方案,兼顾了高速和高精度的特点。

PoP封装技术。目前国内还没有实现先进PoP封装的量产;部分外企在量产Bare Die的PoP封装,海外已经在采用先进的Substrate Interposer技术。

TSV(2.5D/3D)技术。国内TSV的应用主要是CMOS Image Sensor的封装,属于比较低端初级的TSV技术;高端TSV的应用,国内企业正处于研发阶段,国际上,台积电、三星、日月光等国际大公司已具备10微米孔径达到10:1的深宽比的能力。

评论