借力大小核设计架构 多核处理器强效又省电

大小核(big.LITTLE)晶片设计架构正快速崛起。在安谋国际(ARM)全力推广下,已有不少行动处理器开发商推出采用big.LITTLE架构的新方案,期透过让大小核心分别处理最适合的运算任务,达到兼顾最佳效能与节能效果的目的,以获得更多行动装置制造商青睐。

本文引用地址:https://www.eepw.com.cn/article/201610/307666.htm近年行动领域出现重大变革,智慧型手机已成为消费者联网生活的主要工具,然而,这其中涉及各种高效能运算任务如高速网页浏览、导航与游戏,以及语音通话、社群网路和电子邮件服务等效能需求较低的「持续运作,永远连线」后台任务。

与此同时,平板装置也正重新定义运算平台,这些创新设计转变均为消费者打造与内容互动的全新方式,将原本只限于网路共享装置(TetheredDevice)的功能导入行动领域,创造出真正的智慧型新世代运算。

因应电子装置的快速变革,未来半导体向来遵循的摩尔定律(Moore’sLaw)又将如何往下发展?过去,预测晶片的效能每隔18个月就会倍增,而现今电晶体的数量已从数千增加到数十亿个,但若仔细观察单一处理器,就会发现整体的效能几乎呈现停滞不前的情况,这是因为系统能消耗的电量已达到高峰。

克服晶片效能与功耗挑战big.LITTLE设计架构崭露头角

对于未来任何一种处理器,处理速度都将受限于散热问题而无法大幅跃进。任何装置一旦达到热障(ThermalBarrier)就会开始融化,如果是行动电话,便会使装置温度上升造成使用者不适。除物理层面的散热问题外,能源效率也会变得相当差,若调校处理器实作使其速度加快,则所需耗能便会倍数增长,而为增加最后这一丁点的效能,后续导热设计的成本真的很高。

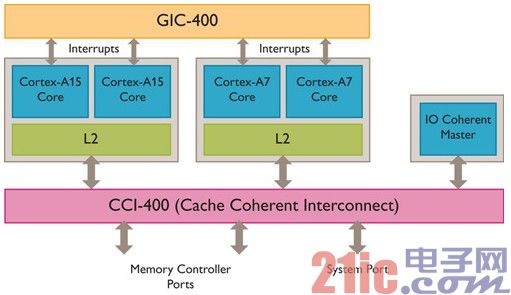

在过去,处理器核心面积倍增代表速度倍增,但是现在面积倍增,速度却只增加几个百分点,因此复杂度并不代表有效率,这就是单一核心系统有所限制的原因之一。如果无法加快单一核心速度,就必须增加独立核心的数量,这也有助于每个核心去应对其被分配到的任务需求,有鉴于此,安谋国际(ARM)遂于2012年提出big.LITTLE处理器架构(图1)。

图1big.LITTLE系统结构示意图

big.LITTLE主要目的在于解决IC设计业界眼前最大挑战,也就是同时提升晶片效能,并延长装置续航力,以延伸消费者「持续运作,永远连线」的行动体验。该技术之所以能达成上述目标,系结合一个大(big)的高效能处理器核心与一个小(LITTLE)的低功耗处理器核心,然后根据效能需求,以无缝连接方式选择合适的处理器。更重要的是,这种动态分配任务的动作,对于上层应用软体或中介软体在处理器上的执行丝毫没有任何影响。

目前已应用于市面上行动装置的big.LITTLE设计,结合高效能Cortex-A15多处理器丛集(Cluster)与具有节能特色的Cortex-A7多处理器丛集。这些处理器在架构上百分之百相容,且均支援40位元实体地址扩展LPAE、虚拟化扩充及NEON、VFP之类的运作单元,无须另外调整即可让针对其中一种处理器类型所编译的软体应用程式,顺利于另一款处理器上运作。

因应任务需求处理器核心无缝切换

big.LITTLE系统结构就快取记忆体一致性(CacheCoherency)的维护而言,无论是同一处理器丛集中的快取记忆体,或是跨不同处理器丛集的快取记忆体,皆保持快取记忆体资料的一致性。这种跨丛集的一致性来自ARMCoreLink快取同调汇流架构(CCI-400,也能提供ARMMali-T604之类的绘图处理器(GPU)系统等元件的I/O一致性)。

两种丛集的中央处理器,还可透过CoreLinkGIC-400之类的共用中断控制器互传讯号。其中,系统包含big.LITTLE切换和big.LITTLEMP(Multiple-Processor)两种执行模式,由于同一应用程式可采用Cortex-A7或Cortex-A15而毋须调整,因此可将应用程式的任务随机对应到正确的处理器上。

切换模式是让不同处理器类型在切换时能进行软体内容的撷取与回覆。以CPU切换来说,丛集中每个CPU在另一个丛集中都有对应的CPU,而软体内容则以CPU为单位,随机在不同的丛集间切换;如果丛集中没有正在运转的CPU,便可关闭整个丛集及相关的L2快取。

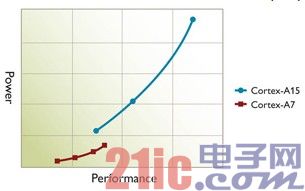

同时,此模式也是动态电压频率调整(DVFS)等能源/效能管理技术的延伸。切换动作类似DVFS操作点的转换,由于处理器上DVFS曲线的操作点,会随负载变化不同而来回变动,当既有的处理器(或丛集)已达到最高操作点,而软体堆叠仍需更高效能,处理器切换动作就会发生,改由另一个处理器执行工作,这个处理器的操作点也会随着负载变化不同而来回变动(图2)。当效能需求不再,可换回之前的处理器(或丛集)。

图2big.LITTLE切换模式DVFS曲线图

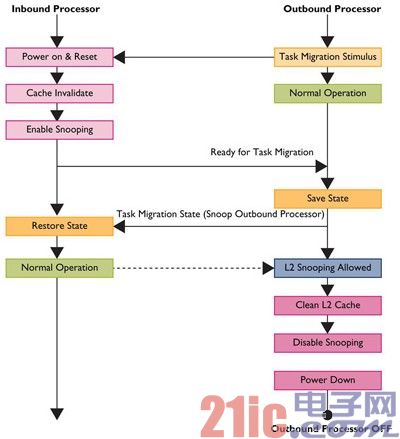

显而易见,一致性是达到加速切换所需时间的关键所在,因为它能让已经储存在离埠处理器(OutboundProcessor)的状态,在入埠处理器(InboundProcessor)上窥探与回覆,而不必透过主记忆体的存取。

此外,由于离埠处理器的L2有快取一致性的功能,当任务切换时,可以透过窥探资料值的方式,改善入埠处理器的快取暖机时间,此时L2快取记忆体仍然可以维持供电状态;不过,因为离埠处理器的L2快取无法提供新资料的快取配置,最后还是必须清除并关闭电源以节省耗电(图3)。

图3big.LITTLE运算任务切换流程图

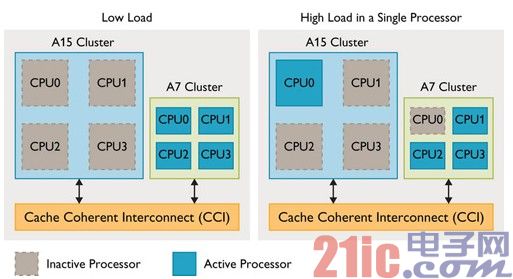

由于LITTLE处理器丛集中,每个处理器都将对应一个big丛集的处理器,因此CPU乃成对配置(Cortex-A15及Cortex-A7处理器上都有CPU0,Cortex-A15及Cortex-A7处理器上都有CPU1,以此类推),不论何时每个配对中只有一个处理器可运转;而系统则会主动侦测各处理器负载,在高负载时将内容执行移到大核心(图4)。当负载从离埠核心移到入埠核心,便会关闭其中一个核心,这种模式让big与LITTLE核心组合能随时运转。

图4big.LITTLE系统CPU切换示意图

[@B]big.LITTLEMP支援非对称丛集运作[@C]big.LITTLEMP支援非对称丛集运作

至于big.LITTLEMP模式则进一步将软体堆叠分配到两个丛集中各个处理器,如此一来,所有CPU皆可同时运作,将系统效能提升到最高点。

由于big.LITTLE系统可经由CCI-400达到快取记忆体的一致性,因此有另一种模式能让Cortex-A15及Cortex-A7处理器同时运作并同步执行程式码,称为big.LITTLEMP,基本上可看作一种异质性多工处理模型。这是big.LITTLE系统最先进且最具弹性的模式,能跨越两个丛集调整单一执行环境。

在这种使用模式下,若执行绪有上述处理效能方面的需求,便可开启Cortex-A15处理器核心并同时透过Cortex-A7处理器核心执行任务。如果没有这方面需求,则只须开启Cortex-A7处理器,在实际应用上,不同丛集的处理器核心不一定一致,而big.LITTLEMP比较容易支援非对称的丛集。

改善低频运算多余功耗big.LITTLE备受瞩目

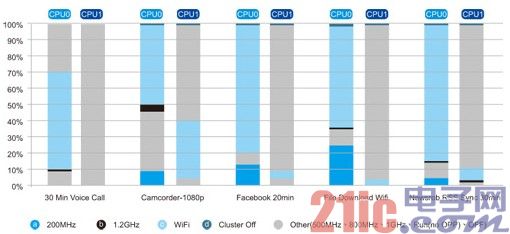

big.LITTLE技术之所以受到IC设计业者瞩目,原因就是一般行动工作量对效能的需求各有不同,必须找到最合适的核心处理。图5显示的是目前搭载Cortex-A9的行动装置中,两个核心在DVFS、闲置与完全关机状态下所花费时间的百分比,(a)处代表最低频率操作点;(b)处则代表最高频率操作点,介于两者之间则属中级频率。

图5低密度使用案例的DVFS驻留时间

除DVFS状态之外,作业系统电源管理也会使中央处理器闲置,图中(c)处代表闲置时间,当CPU闲置的时间够长,系统电源控制软体将完全关闭其中一个核心以节省耗电,图中(d)处便代表这部分。

从图5可清楚看出应用程式处理器在好几种普通工作量下,都有相当多时间处于低频率状态,在big.LITTLE系统里,系统单晶片(SoC)可利用耗能较低的Cortex-A7核心,执行最高操作频率以外的所有工作。以相同方式分析更为密集的工作量,Cortex-A7处理器对应出低于1GHz频率的机会仍然很大。

事实上,自2011年起,使用者层级软体已能在big.LITTLE排程上运转,不过,那只是在处理器核心与互联的软体模型环境上发展。为完整评估big.LITTLE系统效能、功耗及调校是否合宜,还须打造一个能让使用者软体全速运转的测试晶片。

ARM测试晶片早在2012年初夏即由晶圆代工厂完成,并在短短几周内开始搭配参考设计板运转,支援完整版的Linux系统及Android4.0作业系统。这个测试晶片包含一个双核心Cortex-A15丛集、一个三核心Cortex-A7丛集,以及CCI-400快取一致汇流排架构。会影响部分使用者评效基准的绘图处理器并不包括在内,但平台仍可支援Linux、Android作业系统与效能测试软体。

测试晶片的Cortex-A15最高频率达1.2GHz,Cortex-A7则为1GHz。效能评析结果显示,虽然测试晶片上的记忆体系统效能不如big.LITTLESoC量产后的预测水准,但Cortex-A15与Cortex-A7中央处理器的效能仍落在预期范围内。

用来测试big.LITTLE效能的任务量,主要基于Android4.0系统,透过网页进行网路浏览器效能循环,背景则有音效播放。在此实例中均以相当密集的工作量搭配对性能需求不高的背景活动,网路浏览器每2秒便进行网页循环,每页卷动达500画素,因此对系统效能需求相对较高。

这组结论属于较早期的测试结果,用来测试初版big.LITTLEMP修正程式组,将Linux排程程式从一个完整而平衡的排程模式调整成big.LITTLE模式。预期未来在更多业者投入软体修正后,效能与能耗将更进一步改善,而其他可调校的部分也将有相关解决方案被提出。

另外,测试晶片缺少GPU,使CPU的负载高过搭载GPU系统在卸载状态下的负载水准,而在CPU负载较低的状况下,可能会较常使用LITTLE核心,进而达到节能目的。它包含一套基本的电压及频率操作点,但没有对单一处理器核心做独立的电源开关设计,因此big.LITTLE系统单晶片量产后测试结果可望提升。举例来说,后台任务效能便可节省超过70%能耗。

IC设计业者正全力投入big.LITTLE开发,然而,各界最常见的疑问就是应选择哪一种软体模式?目前主要是在CPU切换与big.LITTLEMP之间择一,而两种方式各有正反意见。在CPU切换方面,由于big及LITTLE核心处于搭配成对的状态,因此对称式的拓扑能顺畅运作;而big及LITTLE核心数量不同的非对称式拓扑则须额外的运转。

big.LITTLEMP模式效果更出色

由于Cortex-A7中央处理器核心体积较小,因此可使用四个LITTLE核心加上一到两个big核心,这种作法可能会具有吸引力。从正面角度来看,中央处理器切换让电源及效能的调校更为容易,可重复利用既有的作业系统电源管理程式码,代表实作将有多年的研发及测试结果做为支援。加上不必调整核心排程程式,范围比执行big.LITTLEMP模式更为简化,而软体模式也能日趋成熟。

整体而言,CPU切换是一种极佳解决方案,相关IC设计业者亦正研拟升级至big.LITTLEMP模式,以提供更多元的处理器运算解决方案。big.LITTLEMP具有多项技术优势,虽技术尚未完全成熟,但目前的测试结果已相当不错。由于此模式也支援非对称式拓扑,故毋须调整软体即可完全利用系统中所有核心,对提升晶片效能并降低功耗更有利。

举例来说,big.LITTLEMP能同步利用所有核心在短时间内达到最高效能,或将big与LITTLE核心上的DVFS设定与排程程式设定调成不同状态,以节省更多电力。不过弹性提升仍有其代价,晶片商与系统业者均须增加调校动作,才能从big.LITTLEMP平台获取完整的效能及能耗优势。

这与过去一直为主流,由晶片和晶圆代工厂将作业系统能源管理设定,以及DVFS参数资料,依装置需求转化为行动系统单晶片平台的作法并无太大差异。big.LITTLEMP模式将切换模式延伸并纳入新的参数资料,不仅更为节能,更能为经过效能优化的big核心增加系统回应度。

big.LITTLEMP模式正快速成熟,已有许多晶片商积极投入开发,产品可望在2013下半年大量出炉。由于big.LITTLEMP模式并不须大幅改变硬体,因此晶圆厂可部署支援CPU切换模式的平台,进行核心更新后,再升级到big.LITTLEMP模式,或直接建置现有完整的big.LITTLE平台。

目前big.LITTLEMP相关软体已开始运转,并开始在晶片商研发平台端进行系统测试,ARM与合作夥伴亦正积极进行软体强化,针对各种使用实例将系统效能调校至最佳效果,包括排程程式的负载平衡政策、上下切换点以及执行绪优先秩序等。此外,ARM也在开放原始码平台每月定期推出big.LITTLEMP修正程式组,内含测试晶片平台、测试结果以及说明文件的最新的调校结果。Linaro也已推出修正程式组和CPU切换软体,并开始供应Linaro联盟成员。

随着big.LITTLE技术演进,ARM近期更发布两款具有big.LITTLE处理性能的新型CPU核心--Cortex-A57及Cortex-A53处理器。Cortex-A57是经过效能优化的big核心,每时脉周期的效能较Cortex-A15增加25%,频率效能与能源效率也都高于Cortex-A15处理器。Cortex-A53则为LITTLE核心,每时脉周期效能增加40%,能源效率则等同于Cortex-A7。

布局下世代big.LITTLEARM加速推出新核心

这些新核心在架构上都完全相同,并支援ARMv8架构,因此能导入进阶版的NEON技术与浮点功能、加密加速并支援64位元。除AMBA4ACE,两种核心也都支援新世代快取一致汇流架构,且跟现有ARMv7架构的CPU核心一样,能在AArch32模式下执行既有程式码。支援64位元及额外一般用途暂存器的应用方式洗炼而有效率,且能耗增加不多。

微架构也经过强化,以增加各核心在每个指令时脉周期中的传输量。这些新款核心在经过软体细部升级并支援64位元定址模式后,将会跟Cortex-A15及Cortex-A7处理器一样支援big.LITTLE技术。

两种核心将在2013年提供给合作晶圆厂,预计2014年开始量产。

未来,big.LITTLE设计将为行动装置系统功耗及效能控制点的极度宽动态(WideDynamicRange)带来全新的可能性,这是单一类型处理器核心所无法达到的。目前市面上装置的工作量往往混杂程度高低不同需求的执行绪,这种宽动态便可为其提供完美的执行环境,提供一个在新世代行动平台下,提升装置运算效能并延长续航力的大好机会。

评论