芯片设计中的功耗估计与优化技术

1 引言:功耗在芯片设计中的地位

本文引用地址:https://www.eepw.com.cn/article/201609/303352.htm长期以来,设计者面临的最大挑战是时序收敛,而功耗处于一个次要的地位。近年来,下面的因素使功耗日益得到设计者的关注:

1)移动应用的兴起,使功耗的重要性逐渐显现。大的功耗意味着更短的电池寿命。

2)芯片集成度的提高,使供电系统设计成为挑战。

随着工艺的进步,芯片内的电路密度成倍提高,并且运行在以前数倍的频率之上,而片上连线则越来越细,片上供电网络必须将更多的电力以更少的连线资源送至每个单元,如果不能做到这一点,芯片的稳定性和预定工作频率都将成为问题。IR压降和供电网络消耗的大量布线资源成为困扰后端设计者的重要问题,现在这种压力正在一步步传导到前端设计者的身上,要求在设计阶段减少需要的电力。

3)功耗对成本的影响日益显著

功耗决定了芯片的发热量,封装结构需要及时把芯片产生的热量传递走,否则温度上升,造成电路不能稳定工作。因此,发热量大的芯片需要选择散热良好的封装形式,或者额外的冷却系统,如风扇等,这意味着成本的增加。

基于以上原因,功耗成为产品的重要指标与约束。下面的因素在设计之初,就应当列入设计者的考虑范围:

1)功耗目标的确定

a) 产品的应用领域中功耗指标的商业价值;

b) 封装,制程的成本影响;

c) 实现的可行度,复杂度,由此带来的设计风险和时程影响的评估;

d) 参考值的选取:根据同类产品,经验值,工具分析确定,并随着设计的深入不断修正。

2)优化方案(策略)的设定

在进一步分析之前,我们先看一下功耗的组成。

2 功耗的组成

2.1 core power

功耗的组成包含RAM、ROM、时钟树(clock tree)和核心逻辑电路(Core logic)等四部分,下面依次来分析。

1)RAM

RAM功耗的计算是项复杂的任务,幸运的是,memory compiler可以为我们进行此项工作。关键点在存取每个端口的速率,这可以通过考虑存取pattern类型得到,或者通过仿真得到。建议在设计初期即生成不同参数(宽度,深度,速度,port数)的RAM/ROM的功耗数据,以利于设计探索。

2)时钟树

时钟树的功耗占到整个芯片功耗的40%~60%,因为它的高活动率(100%)和正负边沿均消耗电力。

其中,电容包含寄存器的电容,驱动单元的电容和连线电容三部分。

3)核心逻辑电路

定义核心逻辑电路功耗为除时钟树外的组合与时序单元消耗的电力。由两部分组成:

leakage current

capacitive loads

4)宏单元(macro cell)

多数芯片包含PLL等模拟macro,可以从库提供商的数据手册找到其功耗参数。设计者可以通过切分系统模式关闭不需工作的模块,以减小功耗。

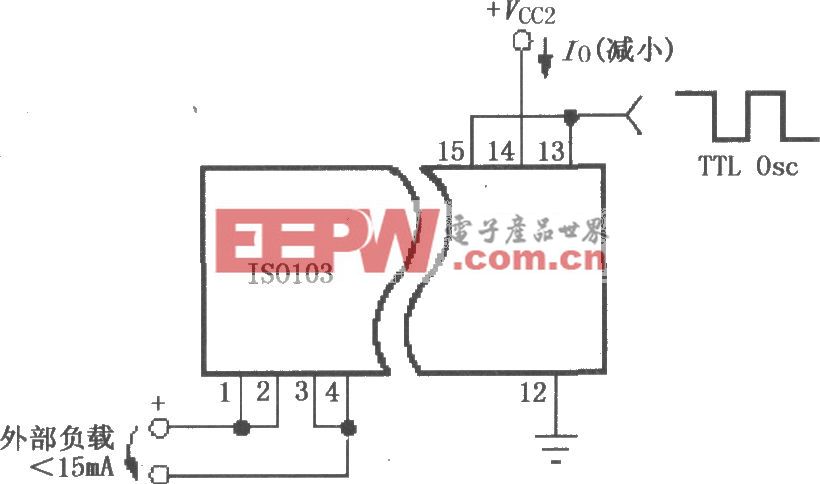

2.2 IO power

IO功耗包含IO单元、外部负载、外部终端等。因为需要驱动板级的连线,IO的电容会是内部单元的数百倍量级,因此消耗较多的电力。有时候,IO的功耗可以占到整体功耗的很大比例,系统架构可能因之改变,如:重新定义系统的划分,以减少芯片-芯片的连接;选择不同的IO接口协议,以减少能量消耗。IO 功耗通常由系统架构,接口带宽与协议要求决定。一旦库选定,设计者可以优化的空间很小,但是核心的功耗是设计者可以减小的,在后面的篇幅中,我们将以核心功耗的估算与优化作为主题。

3 功耗估算

功耗估算的价值是尽可能早地以定量方式看到优化结果,以助于设计者的初期架构探索。在每个阶段, 如产品规划、架构制订、代码书写、综合、PR等,设计者都面临若干选择,能马上看到选择的结果,而不是到设计流程的末尾,可以有效减少开发时间。

3.1估算的方法

功耗的估算可以在设计流程的各个阶段进行,对应设计表征的不同形式。

software level ->behavior level -> RT -> gate -> circuit

越早的阶段,抽象层次越高,其精确度越差,但可以更早给设计者反馈,同时得到估算结果消耗的时间越少。

1. 软件级

首先,定义系统将执行的典型程序。典型的程序通常会有上百万的机器周期,进行一次完整的RTL级的仿真可能需要数月时间,这是不可接受的。解决的方法是在更高层次建立基本组成单元的功耗模型。

比较实用的方法是根据特定的硬件平台,统计出每条指令对应的功耗数据,进行指令级的仿真。

2. 行为级

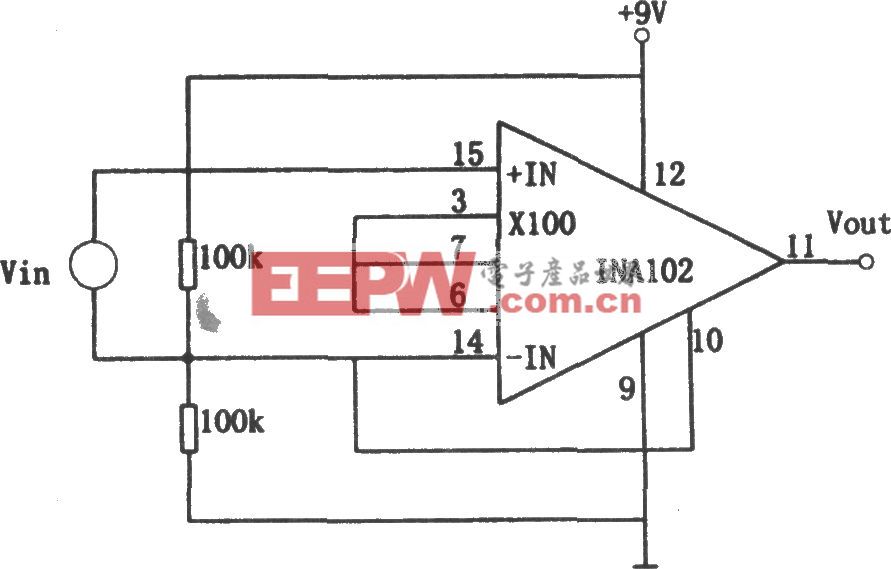

在进行分析前,我们首先应了解电路的功率消耗原理,实际电路的电力消耗如图1所示。

图1

Prms = 1/2 * f * Vdd^2 * sigma(Ci * Ai)

--- f : clock frequency

--- Vdd : voltage

--- Ci is capacitance load of node,

--- Ai is the average switching activity of their node

在行为级设计表征中,物理电路单元尚未建立,难点是得到电容与活动率的值。存在两种思路:

1) 理论估计:

根据电路复杂度得到C,复杂度由算术,逻辑操作的数量,状态的数目与转换率衡量。

complex = f (arith ope, boolean ope, state, transition)

可以根据信息理论估算活动率。

2) 实验估计:

由快速综合得到寄存器传输级的原型,进而估计电容与活动率。

3. 寄存器传输级

第一步是在库中为高层的设计组件建立功耗信息算式,得到方式是在不同环境变量组合下通过仿真,统计功耗数据,绘制成曲线形式。然后,通过静态分析电路结构或动态仿真,收集电路动作几率数据,代入上述算式,得到各个组件的功耗值。最后,把所有组件的功耗值求和,得到总功耗。

4. 门级

与寄存器传输级的区别在于,基本单元是工艺库中的标准单元,功耗方程通过电路仿真得到,所以更精确。

5. 晶体管与版图层

所有的连线的电容、单元的负载,驱动都已得到,根据晶体管和连线模型的电压、电流方程,可以算出精确的功耗数据。

评论