详解ARM Cortex-A32处理器 打造超高能效嵌入式环境

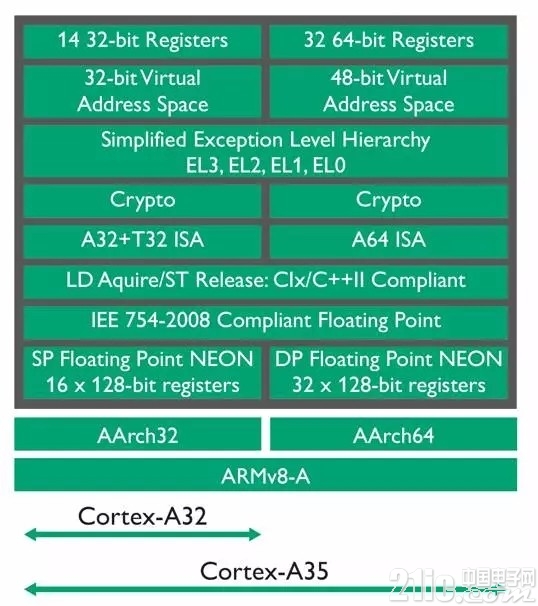

Cortex-A32是ARM架构中独一无二的产品,拥有重要地位。Cortex-A32基于ARMv8-A架构,却是针对32位设计的处理器。下图介绍了Cortex-A32与ARMv8-A架构的匹配程度,并与Cortex-A35进行了对比。

本文引用地址:https://www.eepw.com.cn/article/201609/303274.htm

图一:Cortex-A32和ARMv8-A

基于上述,Cortex-A35可以实现两种执行态,分别为32位AArch32及64位AArch64,从而充分发挥ARMv8-A架构的64位操作能力;相对比,Cortex-A32仅支持32位AArch32执行态,这一决定不仅进一步压缩产品面积,对于不需要64位操作能力的用例,还可以带来显著的功耗优化。

无可否认,部分嵌入式应用可以从64位获益,但许多其他应用都是32位的,将来很长一段时间市场也会依旧如此,Cortex-A32则专为这些应用程序量身打造。

AArch32执行态是早期Cortex-A处理器所用ARMv7-A架构的升级版。尽管不具备64位功能,但在其它某些功能却得到显著增强,使 Cortex-A32与Cortex-A7和Cortex-A5相比更加高效;对基于更早ARM处理器的设计演变,或聚焦嵌入式市场的全新设计来说,都是理想的选择。

对比ARMv7-A,AArch32在如下方面得到强化:

添加多项新指令,密码函数性能提高;

全新的负载获取及存储释放(Load Acquire and Store Release)指令,让访存排序更高效,与全新C++11访存排序语义匹配;

额外的标量和单指令多数据结构(SIMD)浮点指令;

更丰富的系统控制指令。

对比早期的32位ARMv7-A处理器,Arrch32这些额外特性使其具备更佳的性能。

Cortex-A32总线接口上的高级一致性扩展(Advanced Coherency Extensions,ACE)使其可以利用Cortex-A32构建支持完全一致的多处理器系统,按需升级,以实现更高的性能。不过,如果产品面积与功耗是最主要的限制因素,Cortex-A32也提供专门针对单处理器应用优化的版本, 移除一致性逻辑,实现更高功效。

经过大物理地址扩展(Large Physical Address Extension,LPAE),Cortex-A32的可寻址内存空间得到扩展,超过Cortex-A5的32位(4GB),达到40位物理地址空间。

核心本身配置了额外的高级功能,进一步提高效率。其中包括更灵活的功耗管理、更优化的电源域和保留电源门控(retention power gating)的延伸使用。

ARMv7-M 主要特性

ARM Cortex-M处理器基于ARMv7-M架构(Cortex-M0和Cortex-M0+ 采用类似的ARMv6-M架构)。虽然与早期的ARM架构有众多相似之处,但ARMv7-M经过专门打造,更适合深度嵌入、低成本的实时微处理器应用。因此,早期架构的很多功能被删除,并添加了新的特性,以构建更符合“微控制器”环境的编程模式。

对比前代处理器(例如备受欢迎的ARM7TDMI),变化具体如下:

1.操作模式数量显著减少,从7种甚至更多减至2种:仅保留处理器模式与线程模式。其中一种模式(处理器模式)可以默认为优先采用。

2.寄存器文件简化。虽然编程器可用的寄存器数量实质上仍然是16个,但前代架构使用的分组寄存器机制明显减少,因此两种操作模式寄存的只有栈指针(r13)。是否使用寄存拷贝可自行设置。

3.异常模式的变化最为明显。由于典型的微控制器应用可能会出现大量的芯片外设中断,基于此,全新架构中的所有Cortex-M核心都配置了标准嵌套中断向量控制器(Nested Vectored Interrupt Controller,NVIC)。类似的,根据记载处理器地址的向量表,异常处理模式也被标准化。上下文保存和恢复操作完全在硬件中实现,进一步简化编写中断处理器的软件任务。基于上述,实现过程中的干扰性延迟发生几率被降到极低,且高度可预测。

4.与前代ARM处理器类似,ARMv7-M定义了可选内存保护架构。同时,因为裸金属系统或在实时操作系统(RTOS)下运行的系统通常不需要虚拟内存,ARMv7-M并不为其提供支持。

5.为协助实时操作系统(RTOS)的实现和移植,一些标准的片上外围设备也在架构中获得定义,例如SysTick timer。

6.为进一步缩小处理器核心面积,ARMv7-M处理器仅采用Thumb指令集(包括Thumb-2指令集扩展)。

ARMv8-A AArch32 主要特性

Cortex-A处理器基于ARMv7-A或ARMv8-A架构。ARMv8-A处理器支持AArch32执行态,是32位ARMv7-A架构的兼容升级。这些架构的设计添加了专属特性,比如虚拟内存环境,以支持包括Linux、Android、Windows等的平台操作系统。

对比Cortex-M处理器核心,Cortex-A独特之处包括:

1.拥有7种或更多操作模式:用户、管理器、IRQ、FIQ、未定义、中止、系统。每种模式都可以处理一项具体事件,例如,IRQ模式被用于处理IRQ 中断。AArch32还支持另外两种模式:Hyp 和监视器,这两种模式分别用于虚拟化及ARM TrustZone。

2.虽然可以使用的寄存器数量同样是16个,但AArch32有许多与上述操作模式相对应的“分组”(banked)寄存器。一旦进入特定操作模式,这些寄存器就会取代对应的用户模式。这使异常处理的许多方面得到简化,但也意味着需要提高机器管理能力,并在初始化上花更大的功夫。

3.异常模式有显著差别,与最初的ARM架构设备一脉相承。具体来说,向量表是由一组可执行的指令组成,而不是地址,并且保存和恢复上下文的任务几乎完全由编程器承担。

4.还有一个重要差别是内存管理单元(Memory Management Unit ,MMU),内存管理单元会编译核心提交的虚拟地址以及存储系统需要的物理地址。针对Linux一样的平台操作系统所使用的完整需求分页虚拟存储器环境,Cortex-A也可以提供支持。

ARMv7-M 与 AArch32 的不同之处

从基于Cortex-M处理器的系统迁移到基于Cortex-A32处理器的系统时,许多新特性也有必要了解。尽管这两种架构之间有许多相似之处(如寄存器组和指令集存在多种共性),但仍然需要清楚一点,ARMv8-A架构在AArch32执行态下的许多特性是基于早期架构的。本节将详细介绍 AArch32的特性,这些特性在ARMv7-M中不具备,或者实现方式极其不同。

评论