可以将第三方的IP(来自VHDL或Verilog)吸纳到NI Fl

如果适配器模块是由NI公司开发的,那么不需要任何VHDL或其他硬件描述语言的经验。所有的FPGA编程均通过NI LabVIEW FPGA模块和NI-RIO驱动程序软件以图形化的方式完成。如果该适配器模块是由第三方开发的,则或许提供定制的LabVIEW FPGA I/O节点。若存在一个带有套接字的CLIP节点,用户的体验可能会与NI提供的解决方案相似。对于定制设计的适配器模块,设计工程师将需要利用VHDL和XML文件创建一个带有套接字的CLIP节点,以便在LabVIEW FPGA项目中正确表示定制的I/O。

本文引用地址:https://www.eepw.com.cn/article/194265.htm

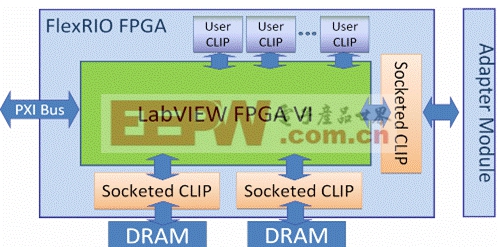

NI FlexRIO中的FPGA利用CLIP节点,集成了第三方的IP核并与适配器模块进行通信

多年前工程师们就已经能够将HDL代码植入LabVIEW框图,以运行与其LabVIEW代码相适应的既有IP。但是,从LabVIEW 8.6 FPGA模块开始,CLIP技术支持工程师们引入第三方的IP并与LabVIEW框图并行执行。这样,第三方IP核可与NI FlexRIO结合使用。

采用FPGA技术有哪些技术优势?

下面列举了FPGA技术的五大技术优势。

高性能

上市时间短

低成本

高可靠性

评论