使用基于FPGA的高速硬件在环仿真器进行电机控制器

介绍

本文引用地址:https://www.eepw.com.cn/article/192074.htm电机在现代生活中扮演着重要角色。出于对安全、成本及效率的考虑,工程师――尤其是混合电动力汽车(HEV)工程师――往往希望在特定的真实环境下通过仿真电机模型对电机控制器进行测试。

由于在经济及环境等方面展现出的优势,HEV受到了广泛的关注,而电机正是HEV的核心部件。尤其是考虑到HEV的电机及电力电子器件体积大, 成本高; 在让控制器去控制这些实际的部件前, 先用硬件在环仿真的方法来测试和验证控制器的性能是非常必要的.

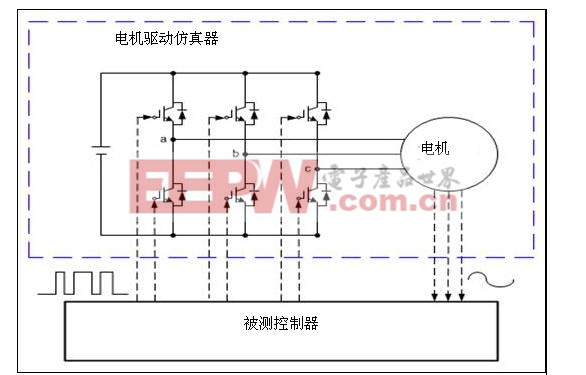

本文讨论基于FPGA而设计的高速HIL仿真器来实现电机控制器测试。下图为HIL测试系统。

电机驱动仿真器包括DC电压源、逆变器桥路以及电机。我们支持永磁同步电机(PMSM)及无刷DC电机(BLDC).

现代电机驱动系统通常由脉冲宽度调制(PWM)所驱动。下图描述了PWM的基本概念。

电机控制器将参考波形与三角载波相比较,从而确定门控制信号的状态。

当时,上面一个电力电子器件的门极控制信号为高, 下面的器件的控制信号为低

当时,上面一个电力电子器件的门极控制信号为低, 下面的器件的控制信号为高

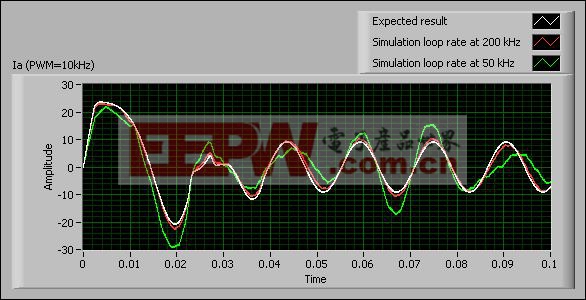

准确检测门信号的开关时刻对仿真器正确产生仿真信号来说非常重要。否则仿真器可能产生抖动、非特征谐波等不准确结果,甚至变得不稳定。下图为PMSM电机驱动的电流波形仿真结果。

PWM频率为10 kHz。可以看到,50 kHz的仿真循环速率还不足以让仿真器及时地检测出开关时刻

因此不能获得精确结果。检测结果中包含了不想要的谐波分量,使结果与期望值偏差很大。而在200 kHz的循环速率下,检测结果就好了很多。

为了获得精确结果,仿真器的采样间隔必须比控制器的PWM周期小很多。如此高循环速率的应用使基于FPGA的方案成为理想选择。我们的定点PMSM模型及定点BLDC模型均能在40个FPGA时钟周期内完成一次更新运算。

提示:有时,期望仿真循环速率可能超过模拟了I/O所能够达到的速率。一般此时无需更新模拟I/O(扭矩输入、电流输出等)来匹配仿真循环率,用户可使用多频编程来保持数字I/O及仿真循环处于高速率,从而用于门信号开关时刻的精确检测,而将模拟I/O设置于另一个循环状态,之后再通过FIFO在两个不同频率的循环间传输数据。

设计的前提假设

a. 电力电子器件的理想开关模型

将电力电子器件建模为理想开关,当门信号为真(高)时,开关为理想的短路电路。当门信号为假(低)时,开关为理想的开路电路。理想开关模型非常适用于系统级仿真,此时我们不关心电力电子器件的寄生效应。此外,理想开关模型可大幅提升仿真速度。

对于电力电子器件的热损失,可以计算其等效电阻,并将此电阻值计入电机的总电阻。

评论