基于FPGA的线阵CCD驱动时序电路的设计

O 引 言

电荷耦合器件(Charge Coupled Deviees,CCD)是一种图像传感器,它在工业、计算机图像处理、军事等方面都得到广泛的应用。目前CCD的应用技术已成为集光学、电子学、精密机械与计算机技术为一体的综合技术,在现代光子学、光电检测技术和现代测试技术领域中起到了相当大的作用。因此,CCD的作用是不可估量的。然而,CCD要正常工作是要驱动时序的,虽然有些CCD往往自带驱动,但是在特殊需要或需要加特殊功能时,CCD驱动往往需要自己设计,例如曝光时间可调等功能。

现场可编程门阵列(Field Programmahie Gate Array,FPGA)是在PAL,GAL,EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

由于FPGA具有易修改,在线编程等特点,可根据不同要求进行在线配置,从而升级方便。另外由于FPGA集成度高,可将系统的部分或全部功能集成在一片芯片上,可减小系统硬件复杂度。

2 CCD工作原理和特性参数

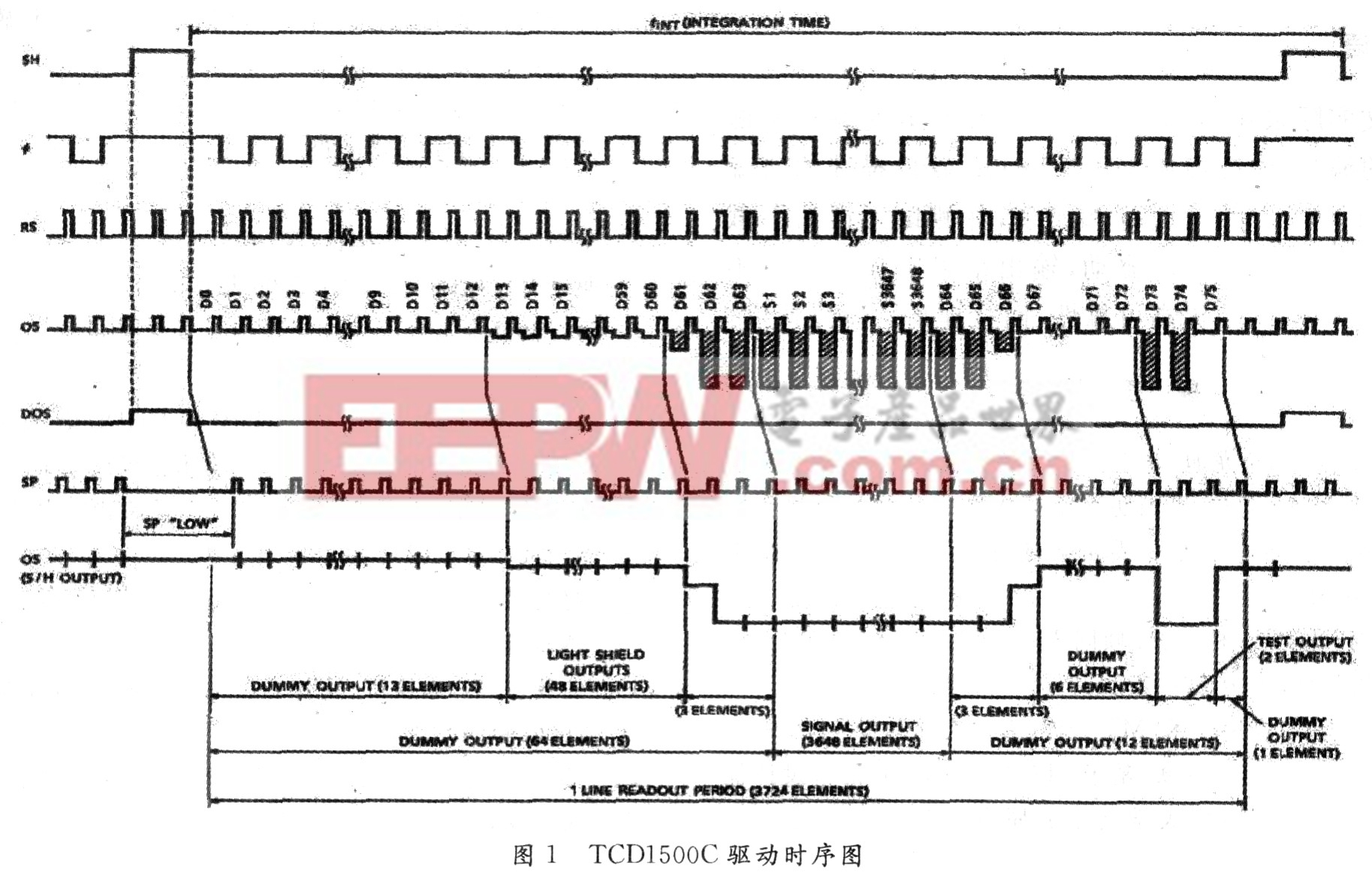

TCDl500C是一种高灵敏度、低暗电流、5 340像元的线阵CCD图像传感器,其像敏单元大小是7μm×7μm×7μm;相邻像元中心距也是7μm;像元总长是37.38 mm。其驱动时序图如图1所示。TCDl500C在驱动脉冲作用下开始工作。

由图1可知,CCD的一个工作周期分为两个阶段:光积分阶段和电荷转移阶段。在光积分阶段,SH为低电平,它使存储栅和模拟移位寄存器隔离,不会发生电荷转移现象。存储栅和模拟移位寄存器分别工作,存储栅进行光积分,模拟移位寄存器则在驱动脉冲的作用下串行地向输出端转移信号电荷,再由SP进行采样和保持,最后由0S端分别输出。RS信号清除寄存器中的残余电荷。在电荷转移阶段SH为高电平,存储栅和模拟移位寄存器之间导通,实现感光阵列光积分所得的光生电荷势阱中,此时,输出脉冲停止工作,输出端没有有效电荷输出。由于结构上的安排,OS先输出13个虚设像元信号,再输出45个哑元像元,然后再输出5 340个有效像元信号,之后再是12个哑元信号,输出1个奇偶检测信号,以后便是空驱动(空驱动的数目可以是任意的)。

2 芯片的选择以及设计平台概述

FPGA选择的是ALTERA公司的FLEXl0K系列的EPFllOKlOLC84一4,他是一款典型在线可编程FPGA器件。

设计选择的平台主要是Modelsire。Modelsim仿真工具是Model公司开发的,它支持Verilog DHL,VHDL以及他们的混合仿真,可以将整个程序分布执行,使设计者直接看到它的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比Quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。仿真都正确无误后再用QuartusⅡ软件来综合和下片。本程序采用Verilog硬件描述语言编写,其可移植性和可读性都好。

评论