基于单片机和FPGA的网络数据加密实现

摘要:介绍了基于单片机、FPGA的网络数据加密实现。整个系统由单片机,FPGA和E1通信接口组成。流密码加密算法采用A5/l和W7算法。采用VHDL硬件语言实现FPGA功能。该硬件加密系统具有较好的安全性。

关键词:通信技术:加密机;FPGA;单片机;VHDL

1 引言

随着信息技术和网络化进程的发展,网络通信安全问题日益突出。现场可编程门阵列(FPGA)以其自身设计灵活、可靠性高的优点广泛应用于加密领域。硬件实现的加密算法不占用计算机资源.加密过程完全与外部总线隔离,具有较高的数据保护能力。算法可灵活改变,具有较强的独立性。加密机由单片机,FPGA和El通信接口组成。FPGA内部算法由VHDL语言编写。该系统适用于要求数据安全较高的场合,其终端可为计算机,银行POS机等,提供数据传输的安全性和保密性。

2 流加密解密原理及算法

2.1 流加密解密原理

流密码由密钥和密码算法两部分组成,密钥一般存储在加解密设备内部,在数据传输前已设置完成。密码算法在较长时间内是不变的。在同步流密码中,只要发送端和接收端有相同的密钥和内部状态,就能产生相同的密钥流。

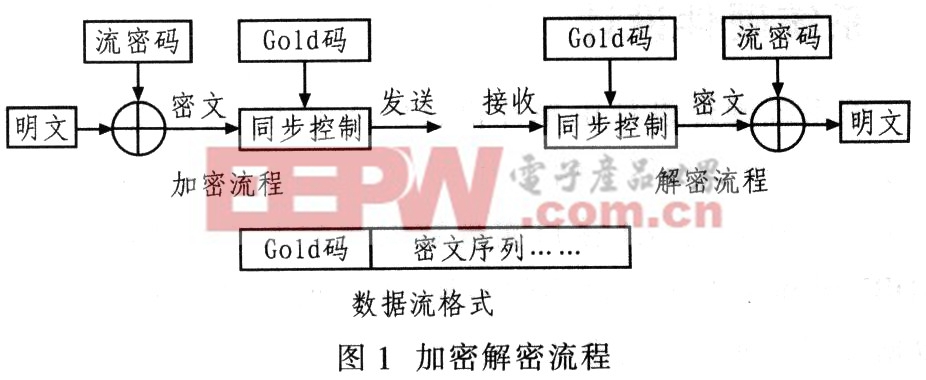

数据传输时,加密端和解密端使用同一个初始密钥,加密时密码流与明文相异或得到密文,同时每隔一定时间加入同步数据;解密时以同步模式产生的密文与密码流进行异或得到明文,同步模式采用63位Gold码。整个加解密过程与发送数据格式如图1所示。在发送密文中加入初始同步码,接收端利用Gold码的三值特性检测Gold码实现同步数据。对接收数据流和Gold码做互相关运算,相关结果满足Gold码的三值特性,说明当前数据流是发送端加入的同步Gold码.标志为密文的起始,然后调用解密算法对后续的密文解密,恢复传输的数据。

pos机相关文章:pos机原理

评论