基于DSP和FPGA技术的低信噪比雷达信号检测

摘要:提出一种基于DSP和FPGA技术的低信噪比情况下雷达信号检测技术的工作原理与硬件实现方法,采用数字化的处理方法处理信息,取代传统使用的模拟检测技术,并对实现的检测方法和关键算法做了详细介绍。

关键词:高速A/D;DSP;FPGA;低信噪比

我国目前的海事雷达大多为进口雷达,有效探测距离小,在信噪比降为3 dB时已经无法识别信号。随着微电子技术的迅猛发展,高速A/D(模拟/数字转换)和高速数字信号处理器件(Digital Signal Proeessors,DSP)、高速现场可编程逻辑器件(Field ProgrammableGate Array,FPGA)的出现,可以在不增加现有雷达发射功率和接收灵敏度的前提下,在信噪比降为3 dB时能测到雷达信号,使雷达的有效作用距离提高。本文主要介绍基于DSP和FPGA技术的低信噪比情况下雷达信号的检测。

1 设计思想

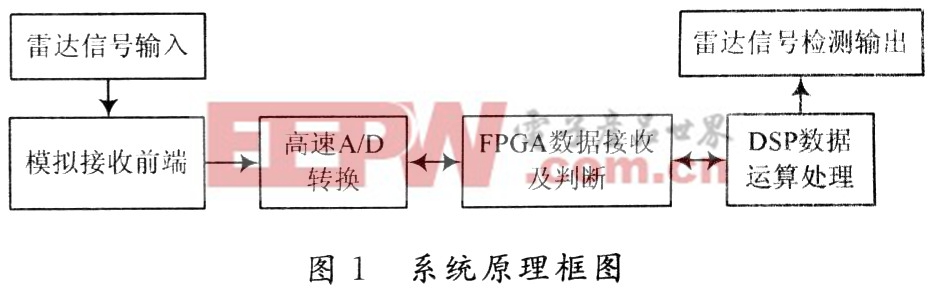

本技术的设计思想主要是通过对接收到的雷达信号进行高速A/D采样,然后利用DSP和FPGA芯片对采样后的信号幅度和轮廓进行判断,以实现低信噪比条件下雷达信号的识别,从而还原出有效信号。系统原理框图如图1所示。

2 系统的硬件设计

2.1 高速A/D设计

大部分雷达信号为射频脉冲信号,常用的工作频率范围为2~18 GHz,脉冲持续时间在几十纳秒到几百微秒。假设检测信号脉宽为150 ns,根据奈奎斯特采样原理,必须选用高速的A/D转换器才不使信号丢失,实际实现需尽可能地多采样数据,才有利于信号幅度和轮廓的识别。经综合考虑,决定每隔8 ns采样一个数据,150 ns可采样18个数据,选用125 MHz的高速A/D转换芯片MAX19541,数据采样位数为12位。MAX19541经过优化,在高于300 MHz的高IF频率时具有优异的动态性能。MAX19541采用1.8 V单电源工作,转换速率高达125 MSPS,功耗仅为861 mW,差分模拟输入可以是交流或直流耦合。该器件还具有可选的片上2分频时钟电路,允许高达250 MHz的时钟频率。这有助于降低输入时钟源的相位噪声,从而获得较高的动态性能,同时采用差分的LVPECL采样时钟,可以获得最佳性能。MAX19541数字输出为CMOS兼容,数据格式可选择2的补码或偏移二进制码,可工作在并行模式,以采样速率从单个并行端口输出数据;或工作在demux并行模式,以1/2采样速率从两个单独的并行端口输出数据。MAX19541的这些优异性能不仅满足高速采样的要求,并且外围器件少,与后级芯片接口简单,无需电平转换。

2.2 FPGA设计

FPGA芯片主要实现数据缓存和电平判断功能,其核心问题为基于用双端口块存储器(Block RAM)的FIFO模块设计和电平判断检测设计。

由于接收机设计的目的是准确实时地处理输入数据,高速A/D的输出必须由高速数字电路处理,否则数字化后的数据就会丢失,或者系统只能工作在非实时模式,所以这些处理方法的计算速度则是目前最为关心的问题。为了能够及时处理高速采样(8 ns)数据,不丢失数据,后继数字处理器件FPGA处理芯片必须选用工作速度高于8 ns的芯片,这里选用了Xilinx公司的SPARTAN XC3S200。Spartan-3 FPGA采用90 nm技术,I/O管脚都支持全SelectIO-Ultra功能,实现了快速、灵活的电接口,足够多的I/O管脚可分别与前级的12位高速A/D转换芯片、后级的DSP处理器相连。该器件具有SRL16移位寄存器逻辑和分布式存储器,能够满足高速大容量的数据缓存和判断处理的需求。FPGA芯片的数据缓存功能基于用双端口块存储器(Block RAM)的FIFO模块设计,容量为负责存储高速A/D转换器转换过来的并行12位数据,供DSP进行数据处理。系统的工作时钟是65 MHz,在实现该模块时,调用COREGenerator来生成FIFO,通过FPGA中的专用双端口块存储器资源,生成的FIFO模块,其存取速度可以达到100 MHz以上,完全满足实际使用的需求。

FPGA芯片的电平判断检测功能在后面的FPGA检测方法中有详细说明。

2.3 DSP设计

DSP处理器负责电平判决门限的运算处理,选用TI公司的TMS320F2812芯片。TMS320F2812提供了强大的计算能力,最高运行速度可达150 MIPS,具有处理性能更强,外设集成度更高,程序存储器更大等特点。TMS320F2812包含了多种芯片,可提供不同容量存储器和不同外设,以满足各种应用的要求。TMS320F2812芯片通过外部地址与数据总线与FP-GA处理芯片相连接。DSP处理器不断从FPGA芯片的FIFO中读出A/D转换后的雷达接收数据,经过运算处理得出噪声的均方根值,再计算出雷达信号的判决门限值写入FPGA芯片的电平接收寄存器中,以进行有用信号的判断处理。

评论