基于FPGA的多通道校准算法的同步实现

数字信号处理模块是接收机系统的核心部分,系统要求数字信号处理模块能实时处理ADC变换后的数字信号,并用软件的方法来实现大量的无线电功能,这些功能包括:多通道校准、编解码、调制解调、滤波、同步、盲均衡、检测、数据加密、传输加密纠错、跳扩频及解扩和解跳、通信环境评估、信道选择等,而单个DSP根本无法完成这些功能。目前可用的一些高速DSP的性能最快的也不超过5GIPS ,与实际需求相差巨大。这种处理资源的匮乏,被称之为DSP 瓶颈[1],因此我们在本系统中主要采用Xilinx的FPGA芯片实现后端数字信号处理。

本文引用地址:https://www.eepw.com.cn/article/191997.htm时钟同步

FPGA硬件设计中,时钟是整个设计最重要、最特殊的信号,异步信号输入总是无法满足数据的建立保持时间,所以需要把所有异步输入都先进行同步化。时钟同步的重要性如下:

● 系统内大部分器件的动作都是在时钟的跳变沿上进行,这就要求时钟信号时延差要非常小,否则就可能造成时序逻辑状态出错;

● 时钟信号通常是系统中频率最高的信号;

● 时钟信号通常是负载最重的信号,所以要合理分配负载。出于这样的考虑在FPGA这类可编程器件内部一般都设有数量不等的专门用于系统时钟驱动的全局时钟网络。

对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。只要可能就应尽量在设计项目中采用全局时钟。FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

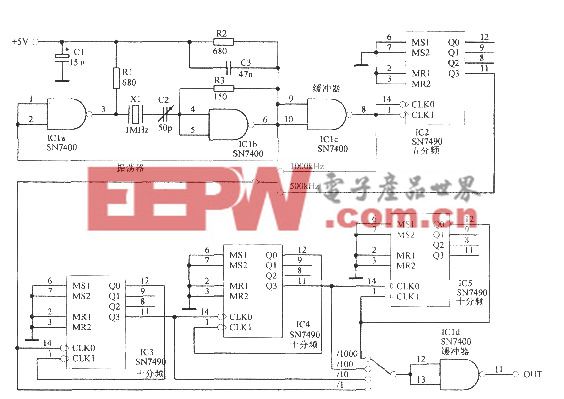

但在许多应用中会出现两个或两个以上非同源时钟,系统设计将面临复杂的时间问题,数据的建立和保持时间很难得到保证。对于需要多时钟的时序电路,最好将所有非同源时钟同步化,即选用一个频率是它们的时钟频率公倍数的高频主时钟。各个功能模块要使用统一的复位电路。在使用带时钟的触发器、计数器等有复位端的库器件时,一般应尽量使用有同步复位的器件。注意复位时应保证各个器件都能复位,以避免某些寄存器的初始状态不确定而引起系统工作不可靠。

基于以上分析,在本设计中,将64M的高频时钟作为系统时钟,输入到所有触发器的时钟端。时钟使能信号Clk_en将控制所有触发器的使能端。即原来接8M时钟的触发器,接64M时钟,同时Clk_en将控制该触发器使能;原接64M时钟的触发器, 还接64M时钟,Clk_en也将控制该触发器使能。这样,就可以将任何非同源时钟同步化。

评论