H.264中二进制化编码器的FPGA实现

1 引言

随着数字电视及视频会议的发展以及应用,H.264由于其更高的压缩比、更好的图像质量和良好的网络适应性而备受关注。

基于上下文的自适应二进制算术编码(CABAC)则作为H.264编码器系统的最后一环,对整个编码性能影响较大。CABAC充分考虑视频流的相关性.能适应信号统计特性的变化,容易达到渐进性能,编码速度较高,但复杂度大,这造成单纯用软件编码难以达到很高的性能,特别是对于高清晰度视频(HDTV)不能实现实时编码,这就需要硬件加速或设计专门的硬件编码电路。

目前,已有相应的硬件加速电路设计问世,但主要是对算术编码部分进行设计,整体性能仍不够理想。这里在对以往加速电路分析的基础上,把握CABAC整个编码原理,主要对其中的二进制化部分进行优化,对相应的二进制化方法进行归类优化,采用并行运算的方案,最终在FPGA上以较优的速度和资源实现硬件编码。

2 二进制化原理

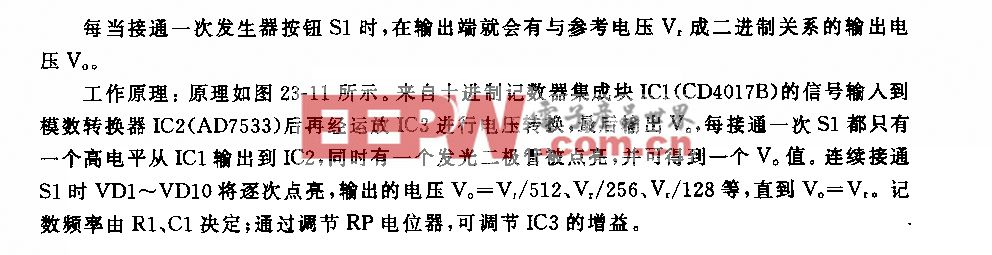

CABAC实现方案包括3个过程:语法元素的二进制化、上下文建模、自适应算术编码,图1是CABAC编码器基本结构。

二进制化是CABAC编码的第1步,提高二进制化模块的编码速度有助于整个系统速度的提高。在二进制化过程中,一个给定的非二进制语法元素被唯一地映射到一个二进制序列(Bin String),其中的每一位称为Bin。

如果输入为给定的二进制语法元素,则此步就可以越过,随后的步骤由编码模式决定。

评论