H.264中二进制化编码器的FPGA实现

2.5 基本二进制转换的串联方案

由以上各种二进制方式可以再推导出3种基本的二进制转换方案。第1种是4位FL前缀与TU后缀(S=2)的串联,而第2和第3种方案来自TU和EGK二进制转换,称为UEGK。这些方案被用于运动矢量微分和变换系数取绝对值。另外语法元素mb_type和sub_mb_type二进制化使用遍历二叉树方法,对应的二叉树已在参考文献中给出。本文引用地址:http://www.eepw.com.cn/article/191909.htm

3 二进制化编码方案优化

H.264标准中的二进制化编码流程是串行的,适合软件的实现,但由于待编语法元素较多,导致执行速度慢且效率低下。而硬件实现的最大优势在于其并行性,可大大提高执行效率。因此,为提高编码速度,在不改变算法实质的前提下,对标准中的编码流程进行相应优化,以利于硬件实现。主要提出以下优化措施:

(1)将语法元素归类按照基本的编码方法及H.264对各语法元素的要求,可将20余种语法元素的二进制编码方法归为6类,包括U二进制化、UEGKO二进制化(k=0,uco-eff=14)、UEGK3二进制化(k=3,ucoeff=9)、宏块/子宏块类型二进制化、宏块量化偏移二进制化,定长与截断串联的二进制化。将语法元素归类,将有效减小编码过程中的繁杂和无序性,有利于编码正常完成。

(2)并行化设计语法元素的二进制化方法可归为8类,在设计中,采用控制单元辨别相应的语法元素,并送入二进制化模块进行编码。但依照H.264标准设计,二进制化单元的入口地址不仅取决于语法元素的值,还取决于语法元素的种类,这种数据依存关系无疑增加了运算量。且输出是串行,不利于流水线设计,这样就将降低系统的时钟频率。故采用一种并行设计方案,以语法元素值为输入,结果得到6个不同的输出,将它们锁存后,利用多路选择器以语法元素种类作为控制端选出所需的值。两种不同的实现方式见图2。

4 二进制化编码的FPGA实现

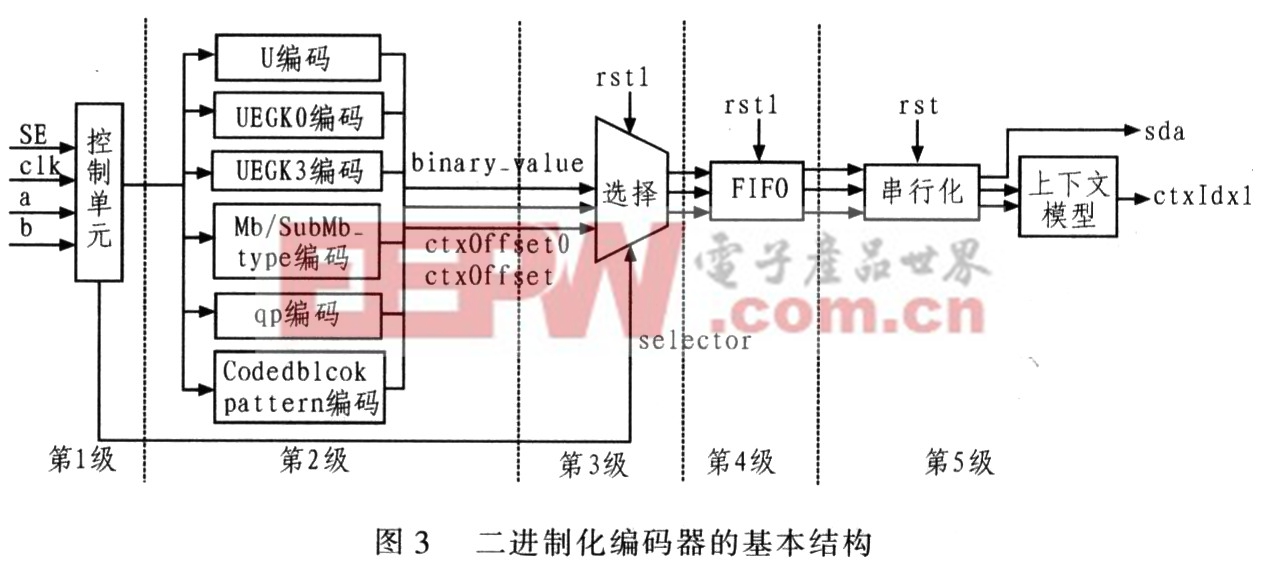

改进后的二进制化编码主要包括:控制单元、二进制化编码单元及选择输出单元,如图3所示。

电路主要分为5级流水线实现。在第1级流水线中,语法元素(SE)、时钟信号(clk)、上下文模型参量(a、b)等输入数据进入控制单元。控制单元采用比较器实现,通过比较给定数值与输入数值的范围确定语法元素的种类,通过种类信号(selector)输出选择所采取的二进制化方式。

评论