基于FPGA的DDS设计

摘要:利用现场可编程门阵列(FPGA)设计并实现直接数字频率合成器(DDS)。结合DDS的结构和原理,给出系统设计方法,并推导得到参考频率与输出频率间的关系。DDS具有高稳定度,高分辨率和高转换速度,同时利用Ahera公司FPGA内的Nios软核设置和显示输出频率,方便且集成度高。

关键词:现场可编程门阵列;直接数字频率合成器;Nios;VHDL

直接数字频率合成DDS(Direct Digital Synthesis)是一种把一系列数字信号通过D/A转换器转换为模拟信号的合成技术。该技术的主要特点:具有超高的捷变速度(0.1μs)、超细的分辨率(可达1μHz)和相位的连续性;输出频率的稳定度及相位噪声等指标与系统时钟相当;全数字化便于单片集成等。基于以上优点,DDS得到广泛应用,但由于其输出带宽小和杂散指标不高,限制了其应用范围。

现有的DDS产品应用于接收机本振、信号发生器、通信系统、雷达系统等,特别是跳频通信系统。这里介绍基于FP-GA的DDS信号源,可在1片FPGA器件上实现信号源的信号产生和控制。将DDS信号源设计嵌入到FPGA器件所构成的系统中,其系统成本不高,但可实现更加复杂的功能。

1 DDS原理

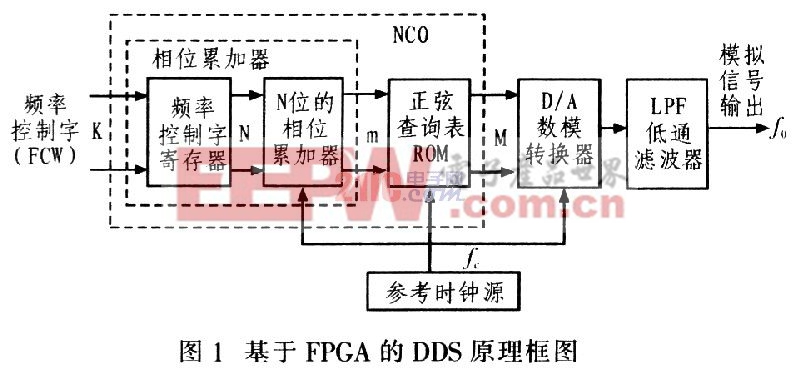

DDS基本结构原理如图1所示,其中数控振荡器(NCO)为FPGA实现部分。其工作原理是:在参考时钟的作用下,相位累加器按照预先设置好的频率控制字进行线性累加,其输出作为波形查找表的地址,通过寻址输出相应的波形幅度码,再由数模转换器将这些数字码变换为模拟电压/电流输出,最后经低通滤波器平滑输出波形。假设要输出的频率是同定的,那么相位增量就是一个常数,在每个时钟周期,相位累加器的数值就按照这个相位增量累加一次,相位增量的大小由频率控制字决定。如果相位增量增大,则相位累加器的增加就比较快,输出的频率就比较高。

假定一个频率为fc的载波,其时域表达式为:

则由式(1)、式(2)看出:C(t)是关于相位的一个周期函数,如果记下一个周期内每个相位对应的幅度值,那么对于任意频率的载波,在任意时刻,只要已知载波的相位φ(t),就可通过查表得到C(t)。

评论