基于FPGA和LabView的遥测信号模拟源设计

摘要:基于FPGA和LabView设计了用于某遥测组件测试的专用设备。运用DDS技术实现传输速率可变的LNDS信号,并使用LabView图形编程工具,实现了数字信号源的交互界面,可以产生由上住机程控信号传输速率和数据内容可变的LVDS信号。

关键词:FPGA;LabView;DDS;LVDS

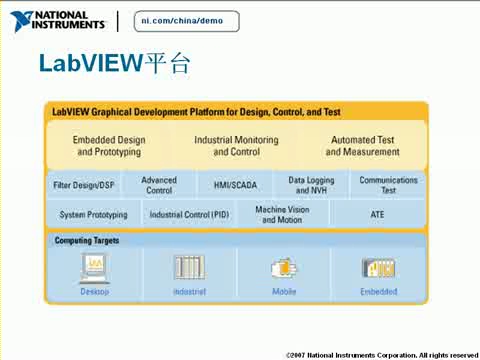

多种高新技术应用于遥测设备中,使得待测信号种类繁多,测试量增大,而且测试时间紧迫、环境复杂多变等诸多因素对测试系统提出了更高要求,不仅要求测试自动化、快速化,而且要求测试系统结构紧凑坚固,抗干扰能力强,具备在复杂环境下工作的能力。基于总线技术的虚拟仪器测试系统架构,能够满足上述要求。PCI总线以其速度高、可靠性强、成本低及兼容性好等性能,在各种总线标准中占有重要地位。FPGA器件具有编程方便、速度快、开发费用低、周期短等特点,受到了广大设计人员的青睐。DDS频率合成技术使输出信号受频率控制码和相位控制码以及参考时钟控制,容易实现调频、调相,输出信号具有高速的频率转换时间、极高的频率分辨率和低相位噪声等优点。基于上述特点,本设计运用DDS技术在FPGA片内实现可变频率方波发送固定格式数据,为了实现一个基于虚拟仪器平台的遥测信号模拟源的设计,下位机与PC通过I/O卡连接。

1 DDS原理及DDS和LVDS在FPGA中实现

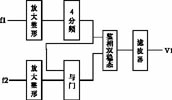

DDS的原理是利用信号的相位与时间成线性关系的特性,通过查表的方式得到信号的瞬时值,从而实现频率合成。DDS的基本原理框图,如图1所示,输出正弦信号频率分辨率为△f=fmin=fclk/2N,其中,fCLK为输入时钟频率;N为累加器的宽度;输出频率为fo=fclk×K/2N,K为频率字的输入值。本次芯片采用Altera公司的CycloneⅡEP2CSQ208C8,设计采用原理图和Verilog HDL相结合的办法实现,本设计中只需在FPGA内部得到可变频率范围4~8 MHz的方波,所以不需要D/A和低通滤波器。

相位累加器采用流水线结构,即在长延时的逻辑功能块中插入触发器,使复杂的逻辑分步完成,减小每个部分的处理延时,从而使系统稳定地运行在较高的频率上。

方波波形存储器直接调用FPGA芯片内部的ROM(2 048×1)模块,前1 024个点为0,后1 024个点为1。为了保证一个地址位对应一个ROM地址,只截取相位累加器22位地址线的高11位与ROM的11位地址线相连。

低压差分信号(Low Voltage Differential Signaling,LVDS)采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接。图2所示为CycloneⅡ器件与INDS接口电路,由差分信号发送器、差分信号互连器、差分信号接受器组成。在实际设计中,要实现一个LVDS发送和接收,只需要在MegaWizard中调用Altlvds并进行定制即可。

评论