基于SOPC基本信号产生器的设计与实现

摘要:介绍一种基于SOPC的基本信号产生器的设计技术,以Altera公司EP1C6Q240C8为硬件核心,把软核CPU嵌入到FPGA之中构成片上系统(SOPC),并结合存储电路、高速DAC电路、LCD电路、键盘电路、JTAG配置电路以及电源电路等进行了硬件电路的设计,以此实现基本信号产生器。阐述了各主要模块设计方案,并给出软硬件测试图。通过示波器观察,满足了系统设计要求,达到预期目标。

关键词:FPGA;SOPC;Nios II;DDS;基本信号产生器

SOPC是以PLD取代ASIC,更加灵活、高效的SOC解决方案。SOPC的设计是通过以IP核为基础、以硬件描述语言为主的设计手段,并借助于以计算机为平台的EDA工具进行的。它代表一种新型的系统设计技术,也是一种软硬件协同设计技术。可以方便地将硬件系统与常规软件集成在单一可编程芯片中。它可编程的灵活性和IP设计的重用性保证了产品的差异性,并缩短面市时间,也无需库存和一次性投片费用,降低了投资风险。所以相对于ASIC具有独特的优势,与ASIC一起形成共存互补的局面。

1 系统设计方案

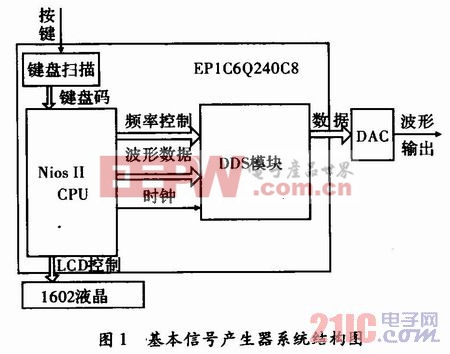

本系统采用以EP1C6Q240C8为核心的设计方案,如图1所示。

方案利用了FPGA优秀的集成特性,把Nios IICPU模块、DDS模块、4×4键盘扫描模块等集成在FPGA上实现,外部只接少量的电源模块、DAC模块以及其他输入输出设备。把传统的完全基于硬件的大部分工作转换成在PC机上通过软件设计编程来实现,减小了系统设计的复杂性。

工作原理如图1所示。外接4×4键盘根据1602液晶显示,通过FPGA的键盘扫描模块向NiosⅡCPU发送键盘扫描码,NiosII CPU根据接收到的扫描码产生相应的信号数据以及控制信号,并通过PIO传送给FPGA中的DDS模块,之后DAC器件将DDS产生的8位信号数据进行数模转换,从而产生任意频率的方波、三角波、正弦波。

2 系统实现

本系统实现主要分3个层次:电路板级设计、FPGA硬件设计以及Nios II软件程序设计。

2.1 电路板级

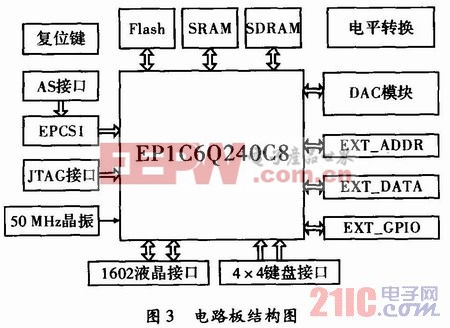

在电路板级设计中,采用Altera公司的EP1C6Q240C8作为设计核心,如图3所示。由于FPGA配置数据掉电后会丢失,所以需要另外搭配一个配置芯片。EPCS1是Altera的专用配置芯片,专门用于存贮对FPGA的配置数据,以保证在FPGA掉电后还能够保存配置信息,再次上电时FPGA芯片会自动从EPCS1中读取数据进行配置。

为了便于功能更新以及扩展,在FPGA外加上Flash、SRAM和SDRAM作为FPGA的程序和数据存储器的扩展,地址线通过EXT_ADDR引出,数据线通过EXT_DATA引出,增加电路的扩展性。

FPGA中DDS模块的双口RAM中输出的数据为8位数字信号,只有通过DAC转换电路才能将数据转换成相应的模拟信号。综合分辨力、转换速度以及接口方式等要求,本设计采用ADI公司的AD9708作为系统DAC器件。AD9708的数据线和时钟线与FPGA的I/O脚连接。AD9708的数字地和模拟地在片内是独立的,应通过外部引脚将其连接在一起。同样,模拟电源和数字电源在内部也是独立的,为了减少来自数字电源的噪声,可在模拟电源输入端串联一个磁珠再与数字电源连在一起。

评论