基于FPGA的可键盘控制计数电路的设计与实现

摘要:介绍一种基于FPGA(Field Programmable Gate Array)现场可编程门阵列的可键盘控制的计数,显示电路的实现方法。应用VHDL语言(高速集成电路硬件描述语言)完成了3x4矩阵开关的扫描电路,可预置数的BCD码计数电路及4位数码管动态扫描电路的描述。通过原理图输入方式完成了系统功能的设计。电路结构简单,便于扩展,可靠性高,且可移植性强,容易实现。该电路已成功应用于测试某脉冲电容质量试验的控制电路中。

关键词:FPGA;键盘扫描;计数;动态显示

FPGA做为现代电子设计技术的核心器件,成为目前硬件设计研究的重点。在工业控制中,计数显示基本电路在仪器仪表中得到了广泛应用,而如何根据需要灵活的设置计数范围,是一个较为复杂的问题。本文应用EDA技术通过对键盘的控制,实现了从0~9999范围内预置数可变的计数显示电路设计。与传统的应用单片机控制键盘扫描的设计方法相比,具有集成度高,稳定度高,抗噪声能力强,容错率低等优点。

1 系统设计原理及电路图

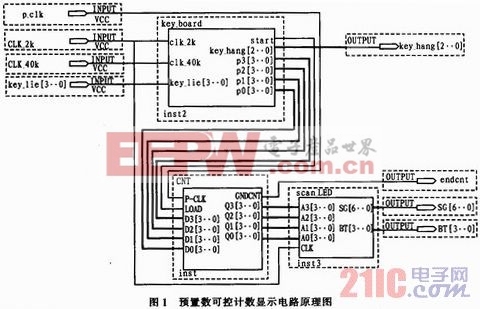

图1为基于FPGA的预置数可控计数显示顶层设计电路原理图,共由3部分组成:键盘扫描控制电路key_board;BCD码计数电路CNT;4位数码管动态扫描显示电路scan_LED。首先,由键盘扫描电路完成对键盘的扫描和键值的译码,当计数电路置数端LOAD为上升沿时,将键盘扫描电路读取的数据经P3-P0并行置入到计数器中做为其计数范围,计数器的输出通过动态扫描译码模块驱动4位数码管显示。

2 VHDL语言的实现

该设计采用层次化设计方法,首先采用VHDL语言完成了对各子模块电路的描述,然后分别将其生成符号元件,通过原理图编辑完成了系统的设计。

2.1 键盘扫描电路

2.1.1 行列式键盘工作原理

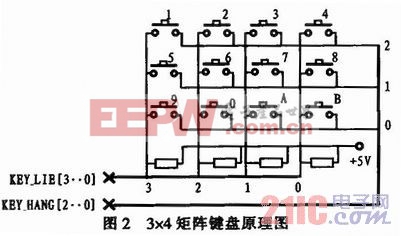

图2为3x4行列式键盘原理图,行线是KEY_HANG[2..0],列线是KEY_LIE[3..0],形成12个交叉点,每个交叉点连接一个按键。12个按键分别对应数字0~9和清零键A,确定键B。当没有按键按下时,所有交叉点断开,由于列线的上拉电阻作用,使其保持高电平。如果行线KEY_HANG[2..0]被设置为低电平,当有按键按下时,该键所在的行线和列线被按键短路,那么相应得列线就变为低电平。

评论