基于FPGA的卷积码编译码器

摘要:基于卷积码的编译码原理,使用VHDL语言和FPGA芯片设计并实现了(2,1,3)卷积码编译码器。其中译码器设计采用“截尾”的Vite-rbi译码算法,在支路量度计算、路径量度和译码路径的更新与存储以及判决与输出等环节的实现中采取了若干有效措施,节省了存储空间,提高了设计性能。最后通过仿真验证了设计的正确性与合理性。

关键词:FPGA;卷积码;编译码器;Viterbi译码器:VHDL

由于卷积码具有较好的纠错性能,因而在通信系统中被广泛使用。采用硬件描述语言VerilogHDL或VHDL和FPGA(Field Programmable Gate Array——现场可编程门阵列)进行数字通信系统设计,可在集成度、可靠性和灵活性等方面达到比较满意的效果。

文献以生成矩阵G=[101,111]的(2,1,3)卷积码为例,介绍了卷积码编码器的原理和VerilogHDL语言的描述方式;文献采用VerilogHDL语言,对(2,1,7)卷积码的Viterbi硬判决译码进行了FPGA设计。本文基于卷积码编/译码的基本原理,使用VHDL语言和FPGA芯片设计并实现了(2,1,3)卷积码编码器及其相应的Viterbi译码器,通过仿真验证了设计的正确性。

1 (2,1,3)卷积码编码器的设计

1.1 (2,1,3)卷积码编码器的原理

卷积码编码器通常记作(n,k,N),对应于每段k个比特的输入序列,输出n个比特;这n个输出比特不仅与当前的k个输入比特有关,而且还与以前的(N-1)k个输入比特有关。(n,k,N)卷积码编码器包括:一个由Ⅳ段组成的输入移位寄存器,每段有k级,共Nk位;一组n个模2加法器;一个由n级组成的输出移位寄存器。整个编码过程可以看成是输入序列与由移位寄存器和模2加法器连接方式所决定的另一个序列的卷积。

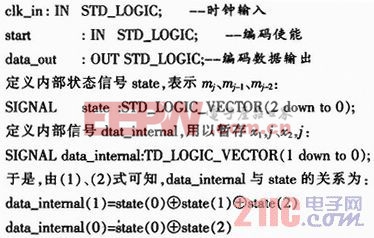

对于(2,1,3)卷积码编码器来说,n=2,k=1,N=3,即每输入1个信息比特时经编码后产生2个输出比特,输出比特不仅与当前的1个输入比特有关.而且还与以前的2个输入比特有关。(2,1,3)卷积编码器框图如图1所示。

当编码使能start为0时不进行编码,并将状态state清零;start为1时进行编码,此时每2个时钟周期输入一个新的信息比特,同时状态信号改变,输出2位已编码比特,即每个时钟周期输出1位已编码比特。

评论