基于FPGA与ARM的遥测数据网络化采集

摘要:现有的遥测接收机为PCI接口,需安装在工控机上使用,为实现设备小型化、便携化,设计实现了小型网络接口遥测解调模块,可配合带有网口的计算机使用。采用FPGA进行遥测数据的帧同步与IRIG—B时码解调,将接收到的遥测数据添加时码后发送给ARM处理器中的Linux系统,并编写Linux 2.6下的FPGA驱动程序,实现FPGA数据的读取,然后通过网卡以TCP/IP格式发给主机,主机实现数据存储与显示。

关键词:FPGA;帧同步;ARM;遥测数据;网络化;Linux

以太网接口通信速度快,传输可靠,使用和配置方便,对于20 Mb/s以下的码速率,100 Mb/s的网卡可以进行不丢包转发,采用TCP包格式还可使设备小型化,便于数据的转发,因此有必要扩展设备的以太网功能。

1 整体模块设计

1.1 系统设计

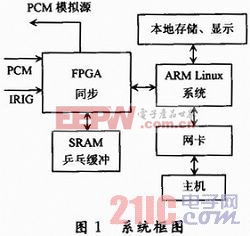

系统设计框图如图1所示。其中,采编器或接收机解调输出的PCM信号及时钟输入到FPGA中进行帧同步,IRIG—B码信息也送到FPGA中进行解调,得到时间信息。数据与时间一起存入SRAM乒乓缓冲区中,达到一定大小后,FPGA向ARM处理器发器中断,ARM中运行的Linux系统,将数据取走,进行TCP/IP打包,发送给接收计算机。

在设备开始工作前,需要在计算机端进行参数设置,计算机TCP/IP包将参数发送给ARM处理器,由ARM处理器转发给FPGA。帧同步器的设计中,码速率为100b/s~10Mb/s,帧长为4~4 096Word,帧同步码组为4~32,ARM网卡为100Mb/s。

1.2 硬件实现

PCB采用6层结构,相邻布线层,水平垂直交叉,电路层与电源层单独分开,提供良好的电磁兼容特性。

1.2.1 FPGA

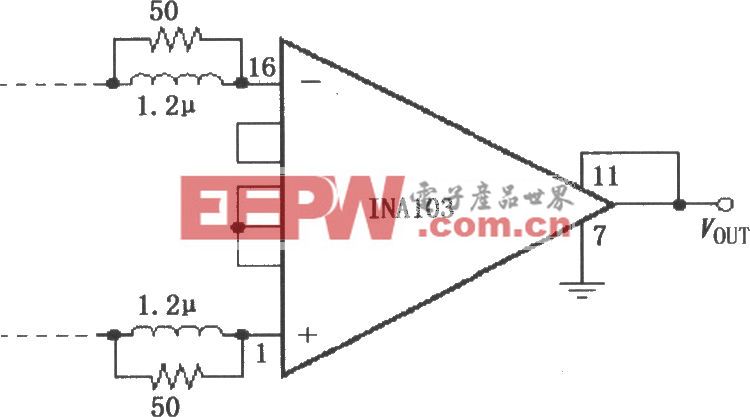

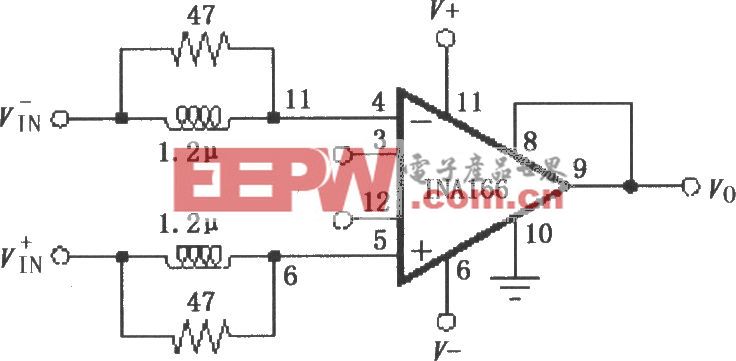

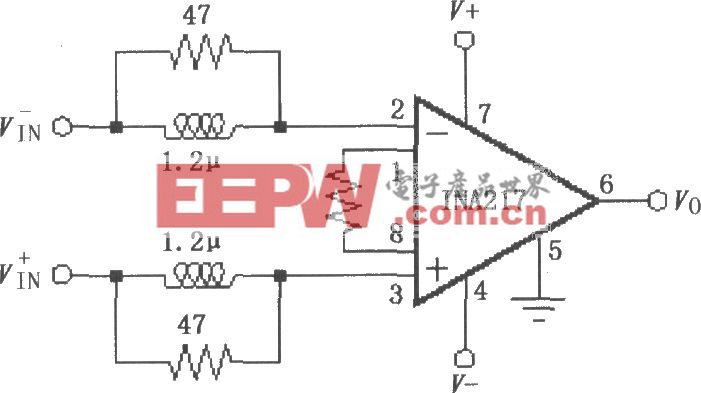

FPGA选择EP1C12,为实现乒乓缓冲结构,采用SRAM为IS61LV25616。输入信号使用SMA线缆连接,在传输过程中会引入衰减,信号输入输出易出现阻抗不匹配的情况,选用AD8556构成射随器,对输入信号进行匹配,同时也增大模拟源的输出能力。

1.2.2 ARM

在此采用S3C2440,内核为ARM920T,最高频率为400 MHz,带MMU支持操作系统。内存采用2×32 MB的SDRAM,存储采用128 MB NAND FLASH,网卡采用DM9000A。

1.2.3 ARM与FPGA的接口连接

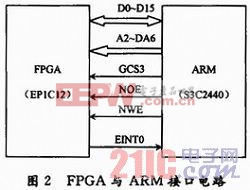

这里采用总线接口,将FPGA作为一个存储设备挂在ARM的存储器总线上,如图2所示。

FPGA在ARM中起始地址为0x18000000,以4 B对齐,占用0x80个地址,地址范围为0x18000000~Ox1800007C,中断为EINT0。

在FPGA内部采用读/写指针来模拟FIFO,用一个地址来读取FPGA数据,其余地址用于配置帧同步器与模拟源的参数。

2 帧同步与B码解调

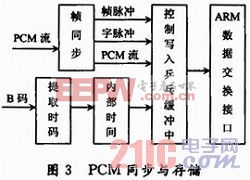

FPGA完成PCM数据的帧同步和解调B码,写入到乒乓SRAM缓冲区中,实现如图3所示。

评论