基于EDMA的FPGA与DSP图像传输的设计与实现

摘要 设计了在FPGA与DSP之间进行图像数据传输的硬件结构,介绍了EDMA的工作原理、传输参数配置和EDMA的传输流程。在开发的实验平台上实现了这一传输过程。借助TI公司的DSP调试平台CCS把接收到的图像数据恢复成图像,验证了传输过程的正确性和稳定性。

关键词 FPGA;DSP;EDMA;图像传输

数字信号处理器(DSP)是采用数字计算方法对信号进行处理的专用芯片。由于其性能稳定,可大规模集成,编程性高和易实现等优点,被广泛应用。其中,以图像处理与DSP技术结合较为普遍,因为图像所包含的信息数据量大,而DSP的处理速度快,易于实现大量数据高速传输的特点能够满足这一要求。

目前,图像处理技术已在通信、信息、电子、航天及军事等领域得到广泛应用。与图像处理有关的系统设计中,FPGA加DSP构架是普遍的使用方法。为充分利用DSP的性能,需要在FPGA中对图像进行相应的预处理,再把图像数据传输给DSP进行处理。所以FPGA与DSP之间的数据传输技术变得不可或缺。

图像数据传输的速度与稳定性对整个系统的性能具有很大的影响。本文介绍了一种基于EDMA的高速稳定的数据传输方法,并在TI的DSP开发平台CCS下,对该方法的性能进行了测试。

1 方案设计

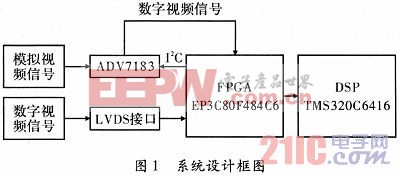

文中图像传输硬件系统结构如图1所示。该系统中采用Ahera公司的Cyclone3系列FPGA:EP3C80F484C6,Analog Device公司的视频解码芯片ADV7183,差分输入14位数据的LVDS接口和TI公司的TMS320C6416。该系统既可采集模拟视频信号,又可采集数字视频信号。模拟信号经过模数转换芯片ADV7183后变成数字信号,数字信号经由LVDS差分接口进入FPGA。为调试方便,模拟图像与数字图像统一使用320×256规格。DSP以EDMA方式接收,经过FPGA预处理后的图像数据,在CCS平台下进行显示以验证传输的正确性。

2 接口电路设计

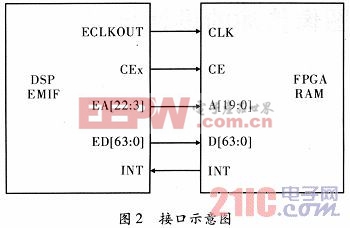

DSP以EDMA方式从FPGA中读取数据,需要FPGA在内部配置一块大小适当的存储空间。FPGA作为一个存储器,通过DSP的外部存储器接口(EMIF)与DSP相连。硬件连接如图2所示。

图2所示为FPGA与DSP的硬件上连接示意图。实际使用时,并没有使用上述所有信号线。FPGA使用到的管脚如下:CLK,CE,A[19:0],D[63:0]和INT。CLK是DSP提供的同步读写时钟,CE是DSP的片选信号,A[19:0]为地址线,D[63:0]地址线。INT为中断信号。

FPGA与DSP的传输机制:FPGA使用QuartusII开发平台往双口RAM中写数,写满后用中断管脚INT来通知DSP读数。DSP收到FPGA的中断信号后,开始读数。读数期间片选信号CE有效,FPGA把DSP片选信号CE作为双口RAM的读使能,在使能期间用DSP提供的时钟CLK读取数据。

系统中DSP提供给FPGA的时钟CLK为100MHz。接收模拟图像时,图像数据为8位,只使用D[7:0]8根数据线;接收数字图像时,图像数据为14位,使用D[15:0]16根数据线,高两位置0。数字图像与模拟图像均为320×256。

评论