捷联惯性组合导航系统的工程设计

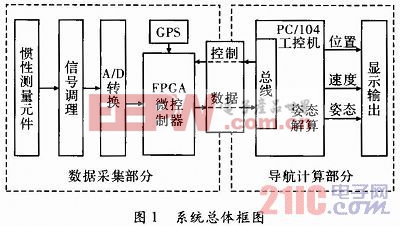

摘要 为适应组合导航计算机系统的微型化、高性能度的要求,拓宽导航计算机的应用领域,文中设计了一种基于PC104和可编程逻辑阵列器件协同合作的导航计算机系统。系统主要包括数据采集模块和数据解算模块两部分,给出了PC104与FPGA的片内接收模块进行通信的设计方案。为提高FPGA与工控机之间的数据传输速度,设计了通过共享双端口RAM的方式,实现了工控机与FPGA之间的高速数据交换。从硬件结构和软件设计方面说明了系统各模块的功能以及模块间的通信。

关键词 组合导航;PC104;FPGA;双口RAM

捷联惯性组合导航系统是一种完全自主的定位导航系统,它可以连续实时地提供位置、速度和姿态信息,短时精度较高,但误差随时间增长而不断积累。GPS导航系统能够全天候提供信息,且误差不随时间积累。因此,将它们组合起来,利用卡尔曼滤波技术进行融合,可以发挥各自优势,提高导航精度。由于捷联系统没有稳定的物理平台,惯性器件测量的数值不能直接进行导航计算,必须先经过大量、实时、精确的数学运算建立起数学平台,才能得到导航参数,在计算上较复杂,对计算机的性能要求高。为减小体积、重量和增加可靠性。文中提出利用PC104嵌入式工控机和FPGA设计一种双CPU结构的捷联惯性组合导航系统。系统中PC/104总线结构的嵌入式工控机来承担姿态解算任务,采用FPGA控制组合系统的采集模块,并利用其内部资源,设计了双口RAM模块、串口接口模块等。双CPU系统使PC104可以专注于解算,保证了系统的实时性。

1 捷联惯性组合导航系统总体方案

捷联惯导系统是将加速度计和陀螺仪沿载体坐标系安装,在进行导航参数计算时,需要是导航坐标系中的量。因此应先将惯性器件测得的比力和角加速度误差补偿后送入计算机进行实时计算,可以得到将比力从载体坐标系转换到导航坐标系的姿态矩阵。通过姿态矩阵可以确定载体的姿态信息。姿态矩阵常用的即时修正方法有欧拉角法、方向余弦法和四元数法,设计采用四元数法。为进行导航解算,选取地理坐标系为导航坐标系,三轴分别指向东向、北向和天向。

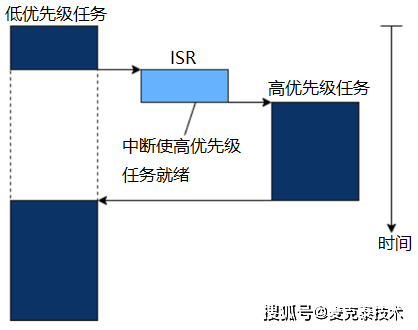

根据捷联惯性组合导航系统的特点,提出采用PC104总线嵌入式工控机的捷联惯性组合导航系统的硬件设计方案,系统包括数据采集和数据解算模块。数据采集模块由FPGA负责控制A/D转换将陀螺仪和加速度计输出的模拟信号转换为数字信号。在FPGA内部开辟一块存储单元,FPGA读取A/D的转换结果存放在内嵌的双口RAM中。FPGA通过双口RAM与PC104进行实时通信,FPGA把采集的数据进行处理后送入双口RAM中,然后发中断信号给PC104,通知其已经有数据可以处理。PC104收到中断信号后,将双口RAM中的数据取走进行处理和解算。FPGA和PC104同时工作,提高了系统的运行速度。系统要求数据采样频率为1kHz,数据解算频率为100Hz,外加时钟频率为40MHz。

2 系统硬件设计

数据采集部分采用Altera公司的EP2C35F672,它是CycloneⅡ系列产品之一,一个LAB中有16个LE,增加了乘法器模块,增强了DSP处理能力。由33 216个LE组成,片上有105个M4K RAM块,片内有35个18 x 18个硬件乘法器,片上有4个PLL,可以实现多个时钟域。PC104总线结构嵌入式工控机具有功耗低、单5 V供电、工作温度范围宽、可靠性高、抗震性好、结构小巧紧凑、浮点运算能力强、运算速度快等显著特点。最适合在嵌入式控制系统中应用。因此它是开发导航计算机的理想方案。

2.1 数据采集模块

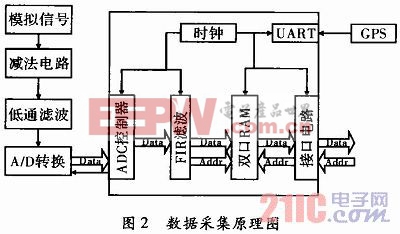

数据采集部分由惯性测量元件、GPS接收机、信号调理部分、A/D转换电路和FPGA控制器等构成。在这部分中,FPGA主要完成同步产生A/D转换的时序,数字滤波和存储经A/D转换后的陀螺和加表的数据。惯性测量元件主要包括3个加速度计和3个陀螺仪,正交安装于坐标系的X轴、Y轴和Z轴,用于提供载体在载体坐标系上的比力和角速度,采用模拟信号输出,加速度计采用差分输出。由于惯性器件安装在一个密闭的容器中,受温度影响也比较大,必须采集温度信号对惯性器件进行补偿。A/D转换电路采用TI公司的A/D芯片ADS1258,ADS1258是一个灵活的、24位低噪声最优化的、快速的、多通道的、高分辨率的模拟/数字转换芯片。24位的精度是0.000 000 06,其理论值较16位A/D有较大的提高。根据芯片资料,ADS1258中的转换器可以提供最大23.7ksample/s的通道扫描速度,可以在700μs的时间里完成一个完整的16通道扫描。模拟电压输入范围为±2.5V。

数据采集部分的功能之一是将加速度计和陀螺仪输出的模拟信号转换为数字信号,并将这一数字信号送入导航计算机。为提高系统的精度,在A/D转换前要先将加速度计和陀螺仪输出的信号进行放大,通过减法电路和低通滤波电路进行调理,然后再通过FPGA控制AD1258进行转换。读取转换数据,利用FPGA内部逻辑设计FIR数字滤波器,将处理后的数据送入FPGA内部的双口RAM,向主CPU发出数据准备好中断。这些由FPGA控制,保证了PC104实时处理和接收到的数据。用FPGA这种纯硬件结构实现的数据采集系统比用MCU等器件用软件控制的数据采集系统速度快,且容易修改。

采集模块的另一个功能是进行GPS数据采集。GPS输出经度、纬度和速度等信息。设计采用Jupitre21 GPS OEM模块,体积小、重量轻、功耗低,首次定位和重新捕获时间短,具有强大的抗干扰、抗遮挡能力。OEM板的输入、输出格式均按RS232串口通信协议,设定为8个数据位,1个起始位,1个停止位,无奇偶校验。GPS接收机数据输出通过RS-232串行口,它信号输出的频率比较低,大约每秒更新一次,接收的数据要完成解码才能用于组合系统的修正。本系统用FPGA实现RS232接口,用于接收GPS的数据。

评论