具有高阻抗并行接口和内部基准电阻的TLC5510解析方

TLC5510是美国德州仪器(TI)公司的8位半闪速架构A/D转换器,采用CMOS工艺,大大减少比较器数。TLC5510最大可提供20 Ms/s的采样率,可广泛应用于高速数据转换、数字TV、医学图像、视频会议以及QAM解调器等领域。TLC5510的工作电源为5 V,功耗为100 mW(典型值)。内置采样保持电路,可简化外围电路设计。TLC5510具有高阻抗并行接口和内部基准电阻,模拟输入范围为0.6 V~2.6 V。

1.1 引脚功能描述

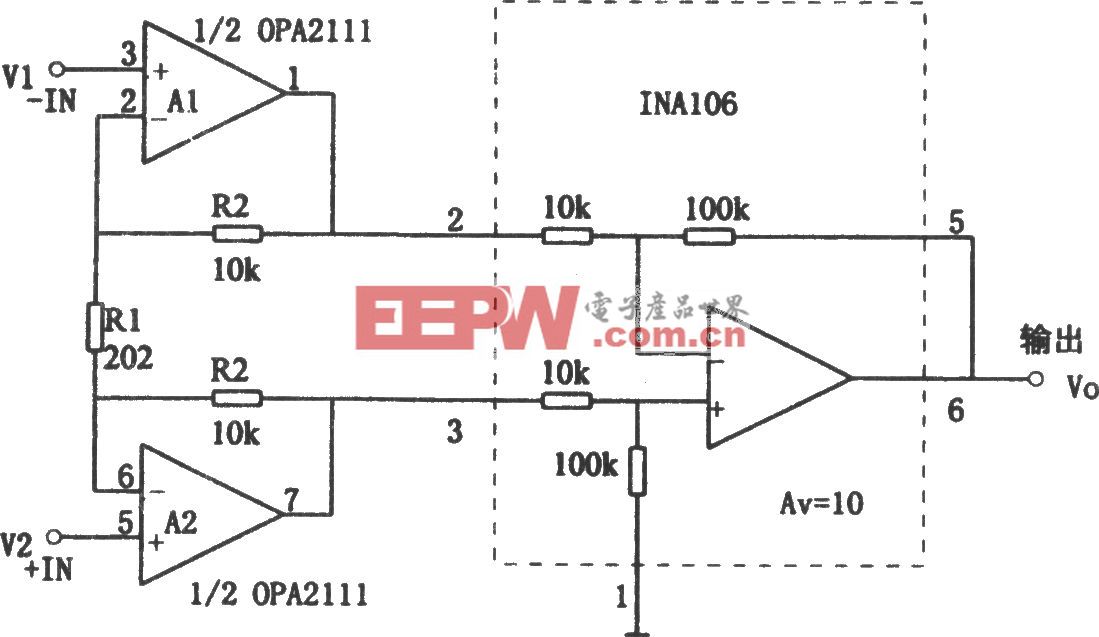

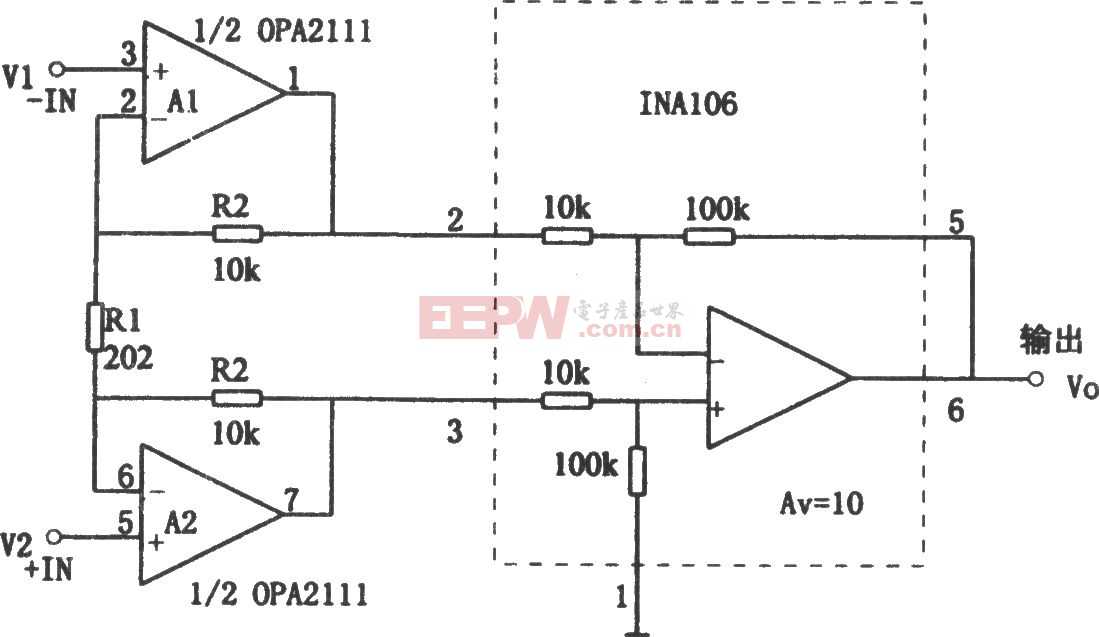

TLC5510采用24引脚的贴片封装,其引脚配置如图1所示。各引脚功能描述如下:

AGND:模拟信号地;

ANGLOG IN:模拟信号输入端;

CLK:时钟输入端;

DGND:数字信号地;

D1~D8:数据输出端。D1为数据低位,D8为数据高位;

OE:输出使能端。OE为低电平时数据端有效,否则数据端为高阻态;

VDDA:模拟电路工作电压;

VDDD:数字电路工作电压;

REFTS:内部参考电压。当内部分压器输出额定2 V基准电压时,该端短路至REFT;

REFT:参考电压(T代表Top为2.6 V);

REFB:参考电压(B代表Bottom为0.6 V);

REFBS:参考电压。当内部分压器产生2 V的额定基准电压时,该端短路至REFB。

1.2 典型应用电路

TLC5510的基准电源有多种接法,根据不同场合选择适当基准电源,利用内部基准源,TLC5510典型应用电路如图2所示。由于其测量范围为0.6 V~2.6 V(即:TLC5510在转换时模拟输入0.6 V时对应数字输出00 000 000,2.6 V对应的数字输出11111 111),因此输入信号在进入TLC5510之前要对其处理,要使该输入信号处于量程内,应加入一个1.6 V的直流分量。

2 基于TLC5510的数据采集设计

2.1 两级采样

TLC5510虽采样率高,但受干扰严重。基于上述特点,将TLC5510运用于宽频数字示波器的数据采集。为了提高抗干扰能力,专门设计一个有源晶振模块为TLC5510提供采样时钟,但导致采样率不可调。为了解决这个问题,采用两级采样。第一级采样为控制A/D转换器对外围的电信号高速采样,并将其采样保存到FPGA内部寄存器,该级采样率恒定不变,并由硬件设计实现;第二级采样为软件采样,即由FPGA采样控制模块从寄存器中提取第一级采集结果,该级采样率是可调的。

2.2 等效采样

根据奈奎斯特定律,采样频率高于信号频率的两倍就可恢复原波形。当采样频率等于或小于信号频率可采用等效采样,在不同周期获取不同相位的幅值,根据相位将幅值连续排列即可复原波形。

采用内触发采样,即由被测信号的某相位点位为触发,然后存储。其实现过程:每一个完整的采样需采集256个点,每一个采样点都是由相同电平触发,触发后启动FPGA内部的计数器,对高频脉冲记数,脉冲数不同,代表相位也不相同。经过256个周期,就可采集256个不同的相位点。

评论