基于FPGA的H.264 DCT算法的硬件实现

摘要:二维离散余弦(DCT)在H.264视频编码中承担者信号从时域到频域变换的作用。在现场可编程逻辑门阵列(FPGA)上设计了高效的采用流水线结构的H.264 DCT硬件电路。首先,把二维4×4 DCT变换转换成二次一维DCT变换;其次,DCT变换之间加一个两端口的RAM,以实现数列的转置;最后,在顶层设计一个有限状态机控制整个流程。该设计采用较少的资源实现了较好的功能,获得了可靠的实验结果。

关键词:二维离散余弦变换;FPGA;H.264;DCT

0 引言

目前,基于分块DCT的编码技术已成为图像/视频编码国际标准的核心技术,一方面是因为DCT具有良好的去相关性和能量压缩性,另一方面是因为DCT具有快速实现算法。随着数字多媒体技术的快速发展,H.264视频压缩标准在多个领域得到了广泛的应用。然而,在当前有限的网络带宽、FPGA有限的资源以及要求更高压缩速率情况下,对二维离散余弦变换(DCT)提出了更高的要求。H.264对图像或预测残差采用了4×4整数离散余弦变换技术,避免了以往标准中使用的通用8×8离散余弦变换、逆变换经常出现的失配问题。

1 H.264的整数DCT变换

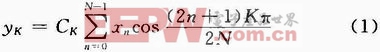

一维N点离散余弦变挽(DCT)可以表示为:

式中:xn是输入时域序列中第n项;yK是输出频域序列中的第K项;系数CK定义如下:

H.264对4×4图像块进行操作,则相应的4×4DCT变换矩阵A为:

![]()

A中的a,b和c是实数,而图像块X中的元素是整数。对实数的DCT,由于在解码端的浮点运算精度问题,会造成解码后的数据的失配,进而引起漂移。H.264比其他图像编码使用了更多的预测过程,甚至内部编码模式也依赖于空间预测。因此,H.264对预测漂移是十分敏感的。为此,H.264对4×4 DCT中的A进行了改造,采用了整数DCT技术,有效地减少计算量,同时不损失图像准确度。式(1)可以等效为:

式中:d=c/b≈0.414;符号![]() 表示结果中的每个元素乘以矩阵E中对应位置上系数值的运算。为了简化计算,去d为0.5,同时又要保持变换的正交性,对b进行修正,取

表示结果中的每个元素乘以矩阵E中对应位置上系数值的运算。为了简化计算,去d为0.5,同时又要保持变换的正交性,对b进行修正,取![]() 。对矩阵C中的第2行和第4行,以及矩阵CT中的第2列和第4列元素乘以2,相应地改造矩阵E为Ef,以保持式(7)成立,得到:

。对矩阵C中的第2行和第4行,以及矩阵CT中的第2列和第4列元素乘以2,相应地改造矩阵E为Ef,以保持式(7)成立,得到:![]()

式中运算![]() 对每个矩阵元素只进行一次乘法,同时它将被归纳到量化运算中。这样,

对每个矩阵元素只进行一次乘法,同时它将被归纳到量化运算中。这样,![]() 中只剩下整数的加法、减法和移位运算。式(8)的矩阵乘法运算可以改造成两次一维整数DCT变换,例如先对图像或其残差块的每行进行一维整数DCT,然后对经行变换块的每列再应用一维整数DCT变换。每次一维整数DCT可以采用蝶形快速算法,以节省时间,如图1所示。

中只剩下整数的加法、减法和移位运算。式(8)的矩阵乘法运算可以改造成两次一维整数DCT变换,例如先对图像或其残差块的每行进行一维整数DCT,然后对经行变换块的每列再应用一维整数DCT变换。每次一维整数DCT可以采用蝶形快速算法,以节省时间,如图1所示。

整数DCT变换是基于DCT的,但是又有一些不同:

(1)它是一个整数变换(所有的操作都可以使用整数算法,而不丢失解码精度);

(2)它可以实现编码端正变换与解码端反变换之间的零误差匹配;

(3)变换的核心部分可以仅仅使用加法和移位操作实现;

(4)变换中的一部分尺度乘法运算可以和量化器结合到一起,减少了乘法的数量。

2 H.264整数DCT变换的FPGA实现

H.264中以4×4块为单位,运算过程中只有移位和加法,降低了算法的复杂度,易于硬件实现。设计时可把二维DCT变换分割为两次一维整数变换,而一维变换可以用蝶形快速算法实现,整个过程只需64次加法和16次移位运算。

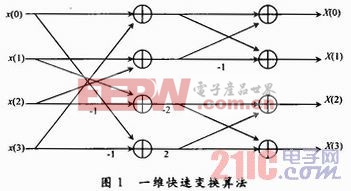

图2为H.264整数DCT变换的框图。首先,输入的数据在控制单元的控制下进行一维DCT变换;然后,将结果存入双端口RAM中,待整个4× 4块一维变换后,将数据按照转置的概念取出,再进行一维DCT变换;最后,将其结果输出即可。在设计中,为了加快系统的速度,采用两个一维DCT变换模块。

2.1 一维DCT蝶形算法模块

根据图1所示的快速算法,在加法器之间插入寄存器,以提高时钟频率和流水线处理,乘法运算可用移位操作,因此可以快速地实现一维DCT蝶形算法。产生的结果存入双端口RAM,以实现二维矩阵的转置。在设计中,为了实现并行处理和最大的速率,设置两个一维DCT蝶形算法模块和4个双端口RAM,在双端口RAM的前后分别设计了数据选择通路。第一个一维DCT实现行变换,第二个一维DCT实现列变换,由于在从行变换到列变换中间经过1个矩阵转置过程,所以在给列变换单元输入数据时,输入的数据需要重新组合后再送给每个列变换单元。

在设计矩阵转置是用4个RAM代替1个RAM,再增加两个4通道的旋转多路器,同时配合对4个RAM的编址读操作,一次输入原始矩阵的一列。并行矩阵转置模块的写操作:每个时钟周期变换一次RAM_BANK的接入顺序,每个RAM_BANK每次写入地址随时钟周期按顺序递增。

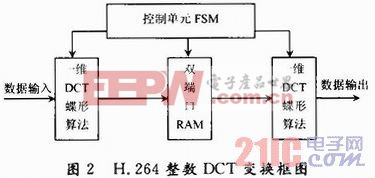

2.2 控制单元FSM

图3显示共有11个状态,主要对2个一维DCT变换模块,4个RAM块和2个数据选择通路进行控制,采用独热编码,较好地实现了各底层模块电路的链接。在设计中,采用异步复位,其好处是:重要综合工具工艺库有可异步复位触发器,那么该触发器的数据输入通道就不需要额外的组合逻辑。同时,采用了专用握手信号实现各模块间有序的数据交换。

3 结论

通过图4可以看出,在50 MHz的时钟频率下电路很好地完成了二维DCT的转换,迟滞也比较小,实验结果与所设计的电路功能完全一致。仿真界面如图5所示。

在Altera的CycloneⅡ平台上,通过QuartusⅡ编译报告可以看出,此电路共消耗了732个LE和256 b的RAM。

4 结语

本文采用高效的流水线结构,并基于FPGA设计实现了H.264硬件电路,无论是硬件占用资源,还是处理精度,完全可以满足H.264视频偏码的需要。

fpga相关文章:fpga是什么

评论