基于FPGA的数字中频接收和恢复系统设计

摘要 介绍一种数字中频恢复系统,该系统分为光纤接收单元、FPGA核心单元和QDUC单元。光纤接收单元采用高速串行器/解串器TLK1501,完成高速串行数据的串行转换。FPGA核心单元对数据进行解码、检验、配置TLK1501和AD9957。QDUC单元实现基带信号的上变频和D/A转换。测试结果证明,系统具有实时性好、工作稳定、抗干扰性强的优点。

关键词 光纤传输;FPGA;数字上变频器

直接数字频率合成(Direct Digital Synthesizer,DDS)作为一种先进的信号产生技术,与传统的频率合成技术相比,DDS具有分辨率高、转换速度快、功耗低和成本低等优点,经过40年的发展,已被广泛用于数字信号处理、软件无线电等领域。在现在的雷达系统中,高速高宽带是现行的趋势,传统的并行传输技术由于存在码间串扰、串音干扰和直流偏移等缺点,难以满足高速高带宽的传输要求。目前国内外有关雷达高速宽带信号接收和恢复技术的研究很广泛,多采用软硬件相结合的设计方式,系统灵活,同时满足信号实时输出的要求。

文中讨论的基于AD9957的多波形雷达信号恢复实现方案,融合了光纤通信、现场可编程门阵列(Field-Programmable Gate Array,FPGA)和DDS等技术,具有误码率低、抗干扰性强、实时性强、数字化、可编程和多功能等特点。

1 系统设计方案

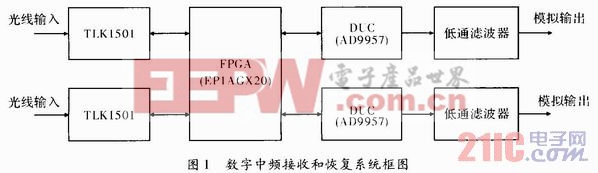

系统的设计结构如图1所示。主要有光纤接收电路、FPGA单元、正交数字上变频器(Quadrature Digital Up Conversion,QDUC)及信号调理电路组成。光纤传输的是已经被编码、校验、成帧后的数据,其接收电路主要由TLK1501电路完成,负责将光电转换后的串行数据流转换为并行数据。FPGA采用Altera公司带有收发器的EP1AGX20CF48416N,完成光纤数据的解帧、校验和解码,剥离出有效的数据。同时,光收发器也可直接与FPGA连接,增强了系统的灵活性。正交数字上变频器(QDUC)采用AD9957实现,完成基带信号的数字上变频(Digital Up Convei ter,DUC)和数模转换(Digital Analog Converter,DAC)。信号调理电路将模拟信号滤波提纯。

2 TLK1501接口设计

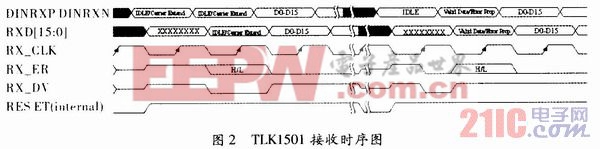

TLK1501是德州仪器推出的0.6~1.5 Gbit·s-1高速串行器/解串器,内部集成了8b/10b编解码模块。TLK1501有两种工作模式,一是收发模式,二是只发模式。在收发模式下,TLK1501的发送和接收需要严格的同步,如果接收侧断开,则发送端自动发送同步码,直到接收侧重新同步。在只发模式下,TLK1501只是单向发送,接收端输出为高阻态。在实际使用中,本系统用到了TLK1501的第一种工作模式,但只用到了TLK1501的接收数据功能。在接收数据时,TLK1501的DINRXP/DINRXN管脚上的高速串行数据流经过串并转换和10b/8b解码后恢复成16 bit并行数据,当RX_DV为高同时RX_ER为低时,在RX_CLK上升沿时,RXD[15..0]端口输出有效数据。应用中TLK1501的接收时序如图2所示。

评论