基于FPGA的星载计算机自检EDAC电路设计

摘要:为了消除空间环境中单粒子翻转(SEU)的影响,目前星载计算机中均对RAM存储单元采用检错纠错(EDAC)设计。随着FPGA在航天领域的广泛应用,FPGA已成为EDAC功能实现的最佳硬件手段。本文介绍了EDAC的编码和实现,提出一种功能完善的、具有自检、自纠错功能的EDAC电路设计,并采用仿真工具对该EDAC电路的功能进行了验证。

本文引用地址:https://www.eepw.com.cn/article/189975.htm1 引言

随着人类对空间探索的深入,空间环境对空间飞行器的电子设备和器件的影响逐渐显现 出来。空间辐射效应,特别是单粒子效应,对空间任务的完成具有潜在的巨大危害。星载计 算机是卫星的核心部件,在空间辐照环境下,必须充分考虑单粒子翻转现象对星载计算机程 控功能的破坏或影响。针对该问题, 目前普遍采用纠错检错(EDAC)设计对星载计算机的RAM 存储单元进行纠错检错处理来消除SEU故障。

EDAC功能可采用硬件和软件两种手段来实现。采用软件手段实现,需要在读写RAM存储 单元时,对存储数据和冗余信息进行计算,因而要占用大量的CPU时间。对于星载计算机而 言,由于CPU器件选型的局限,限制了CPU的性能,使CPU资源非常宝贵,因此目前普遍采用 的是硬件手段来实现EDAC功能。随着FPGA在通信信息特别是在航天领域的广泛应用,FPGA 已成为EDAC功能实现的最佳硬件手段。从目前可获得的资料看,近些年欧美发射的卫星均采 用了FPGA作为星载计算机的核心器件。

2 基于汉明码的传统EDAC设计

2.1汉明编码

目前有许多编码可以用来作为抗SEU的纠错码使用,汉明编码是最常用的EDAC编码,由 Hamming于1950年构造。这种编码可以进行检错和纠错,可以检测1比特和2比特错误,只能 纠正1比特错误,因此适用于单组数据中出现多个错误位概率较低的情况,这恰与SEU经常会 修改星上RAM存储单元1比特信息的情况相符。

汉明编码的实现增加的硬件资源主要是存储器单元,用来存储冗余数据,另外还增加了 编码和解码电路,参加编码和解码的异或门电路随着原始数据位数的增加而线性增加。在处 理性能方面,编码和解码造成一定的延时,增加了存储器的读写时间。

2.2传统的EDAC电路设计

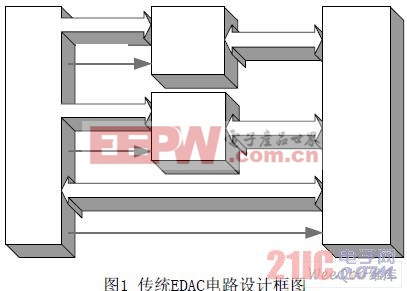

传统的EDAC电路设计仅实现读写功能,基本原理框图如图1所示.写操作时,CPU将数据送入EDAC编码模块中,EDAC编码模块根据该数据生成校验码,并将原始数据和校验码分别写 入数据RAM和校验RAM中;读操作时,CPU将数据RAM和校验RAM中的数据取出,送入EDAC纠错模 块中,EDAC纠错模块将正确的数据送至CPU。这里EDAC编码纠错模块的硬件实现可以是专用 芯片,也可以采用通用的中小规模集成电路搭建。

评论